# QUIESCENT CURRENT REDUCTION OF SELF-COMPENSATED LOW-DROPOUT VOLTAGE REGULATOR

LEE CHU LIANG

FK 2020 15

# QUIESCENT CURRENT REDUCTION OF SELF-COMPENSATED LOW-DROPOUT VOLTAGE REGULATOR

By LEE CHU LIANG

Thesis Submitted to the School of Graduate Studies, Universiti Putra Malaysia, in Fulfillment of the Requirements for the Degree of Doctor of Philosophy

October 2019

# COPYRIGHT

All material contained within the thesis, including without limitation text, logos, icons, photographs and all other artwork, is copyright material of Universiti Putra Malaysia unless otherwise stated. Use may be made of any material contained within the thesis for non-commercial purposes from the copyright holder. Commercial use of material may only be made with the express, prior, written permission of Universiti Putra Malaysia.

Copyright © Universiti Putra Malaysia

Abstract of thesis presented to the Senate of Universiti Putra Malaysia in fulfilment of the requirement for the degree of Doctor of Philosophy

# QUIESCENT CURRENT REDUCTION OF SELF-COMPENSATED LOW-DROPOUT VOLTAGE REGULATOR

By

# LEE CHU LIANG

October 2019

Chair: Roslina Mohd Sidek, PhD Faculty: Engineering

Low-Dropout Voltage Regulator (LDO) is a linear regulator which is mainly used to regulate noiseless supply voltage for analog and Radio Frequency (RF) circuits. Today, the shrinking of transistor size due to the advancement of process technology and the increasing interests in the Internet-of-Thing (IoT) have increased the market demand for portable, wearable and implantable electronic devices. This has driven the need for low power Silicon-on-Chip (SoC) design which includes the integration of LDO into SoC.

Analog and RF circuits have contributed to significantly high percentage of current consumption in low power SoC designs, mainly during stand-by mode. The reduction of quiescent current in analog LDO circuits become very important in order to reduce power consumption and to improve the efficiency of LDO especially during low output load current. Quiescent current is the current needed to keep LDO's internal circuit in vigilant. However, with the absent of large off-chip compensation-capacitor for LDO in SoC, an excessive current is required to maintain ac loop stability of LDO system, especially during low output load current condition.

A self-adjustable current reduction circuit technique has been proposed in this thesis to reduce this unnecessary current when output load current increases from zero value. On top of that, a self-compensation circuit technique is also been proposed to cater the worst case loop stability issue when load current reducing to zero. In this technique, the UGF has been shifted to a lower frequency away from the second pole frequency according to the amount of output load current. It is done using a current feedback circuit, where the total gain is lowered without affecting the location of dominant pole. The self-compensation technique further reduces the total quiescent current, and avoid the excessive current to be used to keep the second pole at higher frequency.

The proposed LDO has been designed and fabricated using 0.13µm CMOS process technology. The results has shown that the proposed LDO exhibits good stability with phase margin more than 60° for all output load condition. The LDO's total quiescent current is only 7.4µA at zero output load current, and 17.7µA at maximum output load current of 100mA. The total quiescent current measurement result on LDO with BGR circuit is 33.1µA, where the BGR consumed 20µA. This LDO is functional at 1.20V supply voltage with 200mV dropout voltage.

Abstrak tesis yang dikemukakan kepada Senat Universiti Putra Malaysia sebagai memenuhi keperluan untuk ijazah Doktor Falsafah

# PENURUNAN ARUS SENYAP PENGATUR VOLTAN PERBEZAAN KELUARAN RENDAH PAMPASAN DIRI

Oleh

### LEE CHU LIANG

Oktober 2019

Pengerusi: Roslina Mohd Sidek, PhD Fakulti: Kejuruteraan

Pengatur voltan perbezaan keluaran rendah (LDO) adalah sejenis pengatur linear yang digunakan terutamanya untuk mengawal voltan bekalan tanpa hingar untuk litar analog dan Radio Frekuensi (RF). Hari ini, pengurangan saiz transistor yang disebabkan oleh kemajuan teknologi proses peningkatan minat dalam *Internet-of-Thing* (IoT) telah meningkatkan permintaan pasaran untuk alat elektronik yang mudah alih, boleh pakai dan boleh implan. Ini telah mendorong keperluan reka bentuk *Silicon-on-Chip* (SoC) kuasa rendah yang merangkumi integrasi LDO ke dalam SoC.

Litar Analog dan RF menyumbang kepada peratusan penggunaan arus yang ketara di dalam reka bentuk SoC kuasa rendah, terutamanya semasa mod *standby*. Pengurangan arus senyap dalam litar analog LDO menjadi sangat penting untuk mengurangkan penggunaan kuasa dan untuk meningkatkan kecekapan LDO terutama semasa arus beban keluaran adalah sangat rendah. Arus senyap adalah arus yang diperlukan untuk memastikan litar dalaman LDO dalam keadaan waspada. Walaubagaimanapun, dengan ketiadaan kapasitor pampasan luar cip yang besar untuk LDO di SoC, arus yang berlebihan diperlukan untuk mengekalkan kestabilan gelung ac sistem LDO, terutamanya pada keadaan arus beban keluaran rendah.

Teknik litar pengurangan arus laras diri telah dicadangkan dalam tesis ini untuk mengurangkan arus yang tidak perlu semasa arus beban meningkat daripada nilai sifar. Di samping itu, teknik litar pampasan diri juga telah dicadangkan untuk menyelesaikan masalah kestabilan gelung terburuk apabila arus beban berkurangkan menjadi sifar. Dalam teknik ini, frekuensi gandaan-uniti (UGF) telah beralih kepada frekuensi yang lebih rendah jauh dari frekuensi tiang kedua mengikut jumlah arus beban keluaran. Ia dilakukan menggunakan arus suap balik di mana jumlah gandaan diturunkan tanpa menjejaskan lokasi tiang dominan. Teknik pampasan diri akan terus mengurangkan jumlah arus senyap, dan mengelakkan arus yang berlebihan untuk digunakan untuk menahan tiang kedua dalam frekuensi yang lebih tinggi.

LDO yang dicadangkan telah direka dan difabrikasi menggunakan teknologi proses CMOS 0.13µm. Hasilnya menunjukkan bahawa LDO yang dicadangkan menunjukkan kestabilan yang baik dengan margin fasa lebih daripada 60° untuk semua keadaan beban keluaran. Arus dalaman LDO hanya 7.4µA pada arus beban sifar, dan 17.7µA pada arus keluaran maksimum 100mA. Jumlah hasil pengukuran arus senyap pada LDO bersama litar *bandgap reference* (BGR) adalah 33.1µA, dimana BGR menggunakan 20µA. LDO ini berfungsi pada voltan bekalan 1.20V dengan voltan perbezaan keluaran sebanyak 200mV.

### ACKNOWLEDGEMENTS

First and foremost, I would like to express my upmost sincere gratitude and heartfelt appreciation to my supervisor, Associate Professor Dr. Roslina Mohd Sidek, for her invaluable advices, technical guidance, great patience and continuous inspiration. I would have never completed my thesis without her motivation and tremendous support. I would also like to thank my co-supervisor, Dr. Nasri and Dr. Fakhrul for their excellent advice and constructive suggestions in helping to shape my project.

The completion of my thesis was made possible with the help rendered by many people. I would like to thank my good friend, Tan Gim Heng who has given me good advice in completing my thesis, and to all the parties who have been working with me during my PhD studies. A special thanks to Mimos Berhad, Mr. Chia CY and Mr. Ayob for supporting me on my die measurement. I am also grateful to all my close friends and family members who always encouraged me in pursuing my studies. Finally, thanks to all those who contributed in one way or another to the success of this research.

This thesis was submitted to the Senate of Universiti Putra Malaysia and has been accepted as fulfilment of the requirement for the degree of Doctor of Philosophy. The members of the Supervisory Committee were as follows:

### **Roslina Mohd Sidek, PhD**

Associate Professor Faculty of Engineering Universiti Putra Malaysia (Chairman)

### Nasri Sulaiman, PhD Senior Lecturer Faculty of Engineering Universiti Putra Malaysia (Member)

### Fakhrul Zaman Rokhani, PhD Associate Professor

Faculty of Engineering Universiti Putra Malaysia (Member)

# ZALILAH MOHD SHARIFF, PhD

Professor and Deputy Dean School of Graduate Studies Universiti Putra Malaysia

Date:

# **Declaration by graduate student**

I hereby confirm that:

- this thesis is my original work;

- quotations, illustrations and citations have been duly referenced;

- this thesis has not been submitted previously or concurrently for any other degree at any other institutions;

- intellectual property from the thesis and copyright of thesis are fully-owned by Universiti Putra Malaysia, as according to the Universiti Putra Malaysia (Research) Rules 2012;

- written permission must be obtained from supervisor and the office of Deputy Vice-Chancellor (Research and Innovation) before thesis is published (in the form of written, printed or in electronic form) including books, journals, modules, proceedings, popular writings, seminar papers, manuscripts, posters, reports, lecture notes, learning modules or any other materials as stated in the Universiti Putra Malaysia (Research) Rules 2012;

- there is no plagiarism or data falsification/fabrication in the thesis, and scholarly integrity is upheld as according to the Universiti Putra Malaysia (Graduate Studies) Rules 2003 (Revision 2012-2013) and the Universiti Putra Malaysia (Research) Rules 2012. The thesis has undergone plagiarism detection software.

Signature: Date:

Name and Matric No.: Lee Chu Liang GS25188

### **Declaration by Members of Supervisory Committee**

This is to confirm that:

- the research conducted and the writing of this thesis was under our supervision;

- supervision responsibilities as stated in the Universiti Putra Malaysia (Graduate Studies) Rules 2003 (Revision 2012-2013) are adhered to.

| Signature:  |                    |  |

|-------------|--------------------|--|

| Name of     |                    |  |

| Chairman of |                    |  |

| Supervisory |                    |  |

| Committee:  | Roslina Mohd Sidek |  |

Signature: \_\_\_\_\_ Name of Member of Supervisory Committee: Nasri Sulaiman

Signature: Name of Member of Supervisory Committee: Fakhrul Zaman Rokhani

# TABLE OF CONTENTS

|                  |                                                          | Page         |

|------------------|----------------------------------------------------------|--------------|

| ABSTRA           |                                                          | i            |

| ABSTRA           |                                                          | iii          |

|                  | WLEDGEMENTS                                              | V            |

| APPROV<br>DECLAI |                                                          | vi<br>viii   |

|                  | TABLES                                                   | xii          |

|                  | FIGURES                                                  | XIII<br>XIII |

|                  | ABBREVIATIONS                                            | XV           |

|                  |                                                          |              |

| CHAPTI           | ER                                                       |              |

| 1 INT            | TRODUCTION                                               | 1            |

| 1.1              | An overview of LDO in Silicon-on-Chip (SoC)              | 1            |

| 1.2              | Motivation                                               | 3            |

| 1.3              | Problem statement                                        | 4            |

| 1.4              | Research objectives                                      | 5            |

| 1.5              | Outline of the thesis                                    | 6            |

|                  |                                                          |              |

|                  | FERATURE REVIEW                                          | 7            |

|                  | Introduction                                             | 7            |

|                  | Performance Characteristics of LDO                       | 7            |

| 2.3              | Review on LDO Topology and Performance                   | 9            |

|                  | 2.3.1 Low Quiescent Current LDO                          | 10           |

|                  | 2.3.2 External Capacitor-less LDO                        | 16           |

|                  | 2.3.3 LDO with Enhancement Topology                      | 20           |

|                  | 2.3.4 Design Trade-off                                   | 25           |

| 2.4              | Summary                                                  | 25           |

| 2 DF             | SICN CONSIDER ATIONS                                     | 27           |

|                  | SIGN CONSIDERATIONS<br>Introduction                      | 27<br>27     |

|                  |                                                          | 27<br>27     |

|                  | Process Technology Considerations<br>Headroom Constraint | 31           |

|                  |                                                          | 31           |

|                  | Power Transistor Design                                  | 32           |

|                  | Load Characteristic and Frequency Response               | 32<br>34     |

|                  | Transient Response                                       | 34<br>35     |

|                  | Inversion Coefficient Methodology                        |              |

|                  | Design Trade-off                                         | 38           |

| 5.9              | Summary                                                  | 39           |

| 4 L0             | W POWER BANDGAP REFERENCE FOR LDO                        | 40           |

| 4.1              | Introduction                                             | 40           |

| 4.2              | Design Methodology                                       | 41           |

|                  | 4.2.1 Matching Issues                                    | 41           |

|                  | 4.2.2 V <sub>EB</sub> of Lateral PNP Transistor          | 43           |

|                  | 4.2.3 BGR Integration with LDO                           | 45           |

| 4.3              | Proposed Low Power Bandgap Reference for LDO             | 46           |

| 4.3.1 Principle of Circuit Operation | 47 |

|--------------------------------------|----|

| 4.3.2 Bandgap Core Circuit           | 48 |

| 4.3.3 Start-up Circuit               | 49 |

| 4.3.4 Output-stage Circuit           | 50 |

| 4.3.5 Op-amp Circuit                 | 52 |

| 4.4 Results and discussions          | 53 |

| 4.4.1 PVT Impact on V <sub>REF</sub> | 54 |

| 4.4.2 Start-up Circuit Operation     | 55 |

| 4.4.3 Bandgap Reference Layout       | 56 |

| 4.5 Conclusion                       | 57 |

#### 5 SELF-COMPENSATED QUIESCENT CURRENT REDUCTION LDO DESIGN 58 51 Introduction 58

| 5.1 | Introduction                                                       | 58  |

|-----|--------------------------------------------------------------------|-----|

| 5.2 | Design Methodology                                                 | 59  |

| 5.3 | Proposed Self-Compensation with Quiescent Current Reduction Design | 60  |

| 5.4 | Circuit Operation                                                  | 63  |

|     | 5.4.1 Error Amplifier and Power PMOS                               | 63  |

|     | 5.4.2 Low Impedance Circuit                                        | 65  |

|     | 5.4.3 Sensing and Control (SAC) Circuit                            | 67  |

| 5.5 | Stability Analysis                                                 | 69  |

|     | 5.5.1 Stability Analysis for High Load Current                     | 71  |

|     | 5.5.2 Stability Analysis for Load Current below 100µA              | 73  |

| 5.6 | Fabrication and Measurement                                        | 75  |

|     | 5.6.1 Layout and Silicon Die                                       | 75  |

|     | 5.6.2 Measurement Plan and Set-up                                  | 76  |

| 5.7 | Results and Discussions                                            | 78  |

|     | 5.7.1 AC Frequency Response and Self-Compensation                  | 78  |

|     | 5.7.2 Quiescent Current Reduction and Efficiency                   | 80  |

|     | 5.7.3 DC Voltage Performance                                       | 83  |

|     | 5.7.4 Transient Response Performance                               | 84  |

| 5.8 | Conclusion                                                         | 85  |

| -   |                                                                    | 0.7 |

|     | NCLUSION AND FUTURE WORK                                           | 87  |

|     | Overview                                                           | 87  |

|     | Technical Contributions and Impact of The Thesis                   | 87  |

| 0.3 | Future Works                                                       | 89  |

|     |                                                                    |     |

|     |                                                                    |     |

| REFERENCES          | 90 |

|---------------------|----|

| BIODATA OF STUDENT  | 98 |

| LIST OF PUBLICATION | 99 |

6

# LIST OF TABLES

# Table

| 2.1: Performance summary on published low quiescent current LDO          | 16 |

|--------------------------------------------------------------------------|----|

| 2.2: Performance summary on published capacitor-less LDO                 | 20 |

| 2.3: Performance summary on published LDO with enhancement topology      | 25 |

| 3.1: 1.2V core transistors I <sub>DSAT</sub> for NMOS and PMOS           | 28 |

| 3.2: 1.2V core transistors Vtlin for NMOS and PMOS                       | 29 |

| 4.1: V <sub>EB</sub> at -40 °C and 125 °C with 10µA and 1µA bias current | 44 |

| 4.2: dV <sub>EB</sub> /dT for 10uA and 1uA bias current                  | 45 |

| 4.3: Component size for bandgap core circuit                             | 49 |

| 4.4: Component size for start-up circuit                                 | 50 |

| 4.5: Component size for output stage circuit                             | 52 |

| 4.6: Transistors size and components value for op-amp circuit            | 53 |

| 4.7: Process variation of V <sub>REF</sub> towards temperature           | 54 |

| 4.8: Measurement results of V <sub>REF</sub>                             | 55 |

| 4.9: Performance comparison of published BGR                             | 57 |

| 5.1: Transistors size for error amplifier and power PMOS                 | 65 |

| 5.2: Transistors size for low impedance circuit                          | 67 |

| 5.3: Transistors size for SAC circuit                                    | 69 |

| 5.4: Measurement results of total current with zero load                 | 83 |

| 5.5: Measurement results of V <sub>OUT</sub> with zero load current      | 84 |

| 5.6: Measurement results of V <sub>OUT</sub> with 30mA load current      | 84 |

| 5.7: Comparison of published results                                     | 86 |

# LIST OF FIGURES

| Figu  | re                                                               | Page |

|-------|------------------------------------------------------------------|------|

| 1.1:  | Structure of a conventional LDO                                  | 2    |

| 1.2:  | 6 1 6                                                            | 2    |

| 1.3:  | LDO design for SoC application                                   | 4    |

| 2.1:  | Hysteretic control LDO                                           | 11   |

| 2.2:  | Schmitt trigger circuit in the hysteretic control LDO            | 12   |

| 2.3:  | High current efficiency digital LDO                              | 12   |

| 2.4:  | Simplified circuit of LDO based on CDL                           | 13   |

| 2.5:  | LDO using adaptive pass transistor                               | 14   |

| 2.6:  | Overshoot reduction and feedback network                         | 15   |

| 2.7:  | LDO using a loop-gain stabilizer technique                       | 17   |

| 2.8:  | CCS in cascoded FVF                                              | 17   |

| 2.9:  | Multiple feedback loops LDO                                      | 18   |

| 2.10: | Hybrid-cascoded compensation circuit                             | 19   |

|       | SR enhancement circuit                                           | 21   |

|       | LDO with active-feedback                                         | 22   |

| 2.13: | Active-feedback circuit                                          | 23   |

| 2.14: | Current efficient LDO with common-gate amplifier                 | 23   |

| 2.15: | SR self-enhancement LDO                                          | 24   |

| 3.1:  | I <sub>D</sub> versus V <sub>DS</sub> for NMOS (W/L=10um/0.13um) | 30   |

| 3.2:  | I <sub>D</sub> versus V <sub>DS</sub> for PMOS (W/L=10um/0.13um) | 30   |

| 3.3:  | I <sub>D</sub> versus V <sub>GS</sub> for NMOS (W/L=10um/0.13um) | 30   |

| 3.4:  | I <sub>D</sub> versus V <sub>GS</sub> for PMOS (W/L=10um/0.13um) | 31   |

| 3.5:  | Example of headroom distribution of a differential amplifier     | 32   |

| 3.6:  | LDO system model with loading                                    | 33   |

| 3.7:  | Transient response of step load current                          | 34   |

| 3.8:  | Inversion Coefficient operating region and summary               | 36   |

| 3.9:  | Operating Plane of MOS transistor                                | 37   |

| 3.10: | Effective gate-source voltage versus Inversion Coefficient       | 38   |

| 4.1:  | Integration of proposed BGR and LDO                              | 40   |

| 4.2:  | BGR mismatched components due to process variation               | 42   |

| 4.3:  | Simulated PNP V <sub>EB</sub> versus temperature                 | 44   |

| 4.4:  | PVT impact of $\Delta V_{REF}$ to $\Delta V_{OUT}$               | 45   |

| 4.5:  | Proposed schematic of low power BGR for LDO                      | 46   |

| 4.6:  | Typical V <sub>REF</sub> versus temperature                      | 47   |

| 4.7:  | PTAT and CTAT voltage reference                                  | 48   |

| 4.8:  | Bandgap core circuit                                             | 48   |

| 4.9:  | Start-up circuit                                                 | 50   |

| 4.10: | Output stage circuit                                             | 51   |

| 4.11: | Two-stage op-amp circuit                                         | 52   |

|       | V <sub>REF</sub> versus temperature                              | 54   |

|       | $V_{REF}$ dependency on transient ramping $V_{DD}$               | 55   |

|       | $V_{REF}$ dependency on DC sweep on $V_{DD}$                     | 56   |

|       | The bandgap reference layout                                     | 56   |

| 5.1:  | Conceptual LDO design in SoC                                     | 58   |

| 5.2:  | Proposed conceptual LDO design                                   | 60   |

| 5.3:  | Complete schematic circuit of the proposed LDO                   | 62   |

|       |                                                                  |      |

$\bigcirc$

| 5.4:  | Error amplifier with M <sub>P</sub> and feedback network          | 63 |

|-------|-------------------------------------------------------------------|----|

| 5.5:  | Low-impedance circuit                                             | 66 |

| 5.6:  | Sensing and control (SAC) circuit                                 | 68 |

| 5.7:  | Proposed LDO open-loop configuration                              | 70 |

| 5.8:  | Bode plot during high ILOAD                                       | 72 |

| 5.9:  | Bode plot during very low ILOAD                                   | 74 |

| 5.10: | Physical layout of the proposed LDO                               | 75 |

| 5.11: | Die picture of proposed LDO                                       | 76 |

|       | Measurement set-up configuration                                  | 76 |

| 5.13: | Pads allocation in silicon die                                    | 77 |

| 5.14: | Probe station                                                     | 77 |

| 5.15: | Frequency response at high ILOAD                                  | 78 |

| 5.16: | Frequency response at I <sub>LOAD</sub> below 100µA               | 79 |

| 5.17: | UGF versus I <sub>LOAD</sub>                                      | 80 |

| 5.18: | PSRR at different ILOAD                                           | 80 |

| 5.19: | I <sub>21</sub> at low-impedance circuit versus I <sub>LOAD</sub> | 81 |

| 5.20: | Quiscent current versus ILOAD                                     | 81 |

| 5.21: | Efficiency versus ILOAD                                           | 82 |

| 5.22: | V <sub>OUT</sub> versus temperature                               | 83 |

| 5.23: | V <sub>OUT</sub> versus I <sub>LOAD</sub>                         | 84 |

| 5.24: | Line transient response                                           | 85 |

| 5.25: | Load transient response                                           | 85 |

|       |                                                                   |    |

xiv

C

# LIST OF ABBREVIATIONS

| BGR                |

|--------------------|

| BJT                |

| CMOS               |

| CTAT               |

| EA                 |

| Gm                 |

| G <sub>ND</sub>    |

| IC                 |

| IoT                |

| LDO                |

| MOSFET             |

| NMOS               |

| OTA                |

| p <sub>-3dB</sub>  |

| PMOS               |

| PNP                |

| PTAT               |

| PVT                |

| SAC                |

| SoC                |

| TC                 |

| UGF                |

| V <sub>DD</sub>    |

| V <sub>DS</sub>    |

| V <sub>DSAT</sub>  |

| V <sub>EB</sub>    |

| V <sub>GS</sub>    |

| $V_{\text{SD}}$    |

| V <sub>SDSAT</sub> |

| V <sub>SG</sub>    |

|                    |

$V_{\text{TH}}$

| Bandgap Reference                       |                             |

|-----------------------------------------|-----------------------------|

| Bipolar Junction Transisto              | ~*                          |

|                                         |                             |

| Complementary Metal Ox                  |                             |

| Complementary to Absolu                 | ute Temperature             |

| Error amplifier<br>Transconductance     |                             |

| Ground                                  |                             |

|                                         |                             |

| Integrated Circuit<br>Internet-of-Thing |                             |

| e                                       |                             |

| Low-Dropout Regulator                   | tor Field Effect Transistor |

| N-Channel MOSFET                        | tor Field Effect Transistor |

| Operational Transconduct                | tance Amplifier             |

| Dominant pole                           | ance Amphilier              |

| P-Channel MOSFET                        |                             |

| P-type Bipolar Junction T               | ransistor                   |

| Proportional to Absolute 7              |                             |

| Process-Voltage-Tempera                 |                             |

| Sensing and Control Circu               |                             |

| System on Chip                          |                             |

| Temperature Coefficient                 |                             |

| Unity Gain Frequency                    |                             |

| Voltage Drain Drain                     |                             |

| Drain-Source voltage                    |                             |

| Saturation Drain-Source v               | voltage                     |

| Emitter-Base voltage                    |                             |

| Gate-Source voltage                     |                             |

| Source-Drain voltage                    |                             |

| Saturation Source-Drain v               | voltage                     |

| Source-Gate voltage                     |                             |

| Threshold voltage                       |                             |

|                                         |                             |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 An overview of LDO in Silicon-on-Chip (SoC)

In recent years, the market demand for portable and wearable electronic devices have been driven by the technology revolution trend such as Internet-of-Thing (IoT) and biomedical engineering. The IoT trend has enabled the possibility of many household electrical appliances and portable electronic devices to be connected through internet cloud (Zarate-Roldan, Carreon-Bautista, Costilla-Reyes, & Sanchez-Sinencio, 2015; Koay & Chan, 2017). The wireless communication integrated circuit (IC) devices such as the Radio Frequency integrated circuits (RF ICs) may need standalone power source and the devices itself are required to be low power consumption (Zeng & Tan, 2016). On biomedical technology trend, a convenient portable and wearable devices which is normally used for all hour wireless monitoring on the medical condition of patients are demanding (Goldstein, Kim, Xu, Vanderlick, & Culurciello, 2012; L. Y. Wang, Li, & Wu, 2012; Elzeftawi & Theogarajan, 2013). Long hour operation sustainability devices can be realized with low power consumption chips set and low count number of on board components which consume higher current. With the advancement of today's nanotechnology and Micro-Electro-Mechanical Systems (MEMS) technology, the implantable IC has come into reality (Ramos, Ausin, Duque-Carrillo, & Torelli, 2011; Zou & Larsen, 2011; Kok, Huang, Zhu, Siek, & Lim, 2012; Jalalifar & Byun, 2013). In order not to generate any harmful heat on the patients' body, a very low power operational implantable IC chips are therefore required (S.-Y. Lee, Yang, Hsieh, & Fang, 2010; Narasimhan, Chiel, & Bhunia, 2011; Lotfi Navaii, Jalali, & Sadjedi, 2012). All these demands have driven the design trend of low power consumption IC. Furthermore, the shrinking of transistor size in advance process technology nowadays has enabled the full functional circuitry system to be built on a single chip, namely System on Chip (SoC). The SoC methodology not only improved the performance of the circuitry, it has also reduced the number of off-chip components, hence reduces the overall power consumption and cost (W.-M. Chen et al., 2014; L. M. Chen et al., 2015). By and large, these technology trends have further enhanced the demand on low power consumption IC chips with SoC methodology. On the end consumers' point of concern, low power SoC trend is the main factor where the electronic gadgets nowadays are able to sustain longer hours of operation (Y. Park & Salman, 2016).

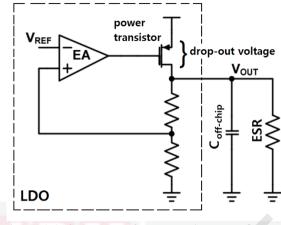

Low dropout linear regulator (LDO) is one of the most important unit of the power management module (Paul et al., 2016). LDO is usually used to regulate analog or RF circuit modules. Before the trend of SoC taken place, LDO was designed in a single module. The structure of a conventional LDO configuration is shown in Figure 1.1 (Gjanci & Chowdhury, 2011; Márquez et al., 2017). An error amplifier (EA) is used to drive the power transistor. An off-chip capacitor that connected to the output of LDO which comes with its equivalent series resistance (ESR) is used for loop stability compensation of the LDO. With the large capacitance value of the passive component capacitor, the loop stability of LDO module can be easily achieved.

Figure 1.1: Structure of a conventional LDO

In today's low power environment IC chips, power management unit is integrated in a single SoC. The off-chip capacitor is removed and the LDO is integrated into the SoC. However, implementing a large capacitor in silicon will need a very high silicon cost. Therefore, this has created a problematic issue for LDO stability compensation. As such, the dominant pole of LDO has also been shifted to internal circuitry of LDO from its output node (C.-J. Park, Onabajo, & Silva-Martinez, 2014). For low power SoC design, the supply voltage source has decreased to 1.20V or lower for deep submicron process technology smaller than  $0.13\mu$  m. Whereby the drop-out voltage of power PMOS transistor hasn't been reduced much due to the constraint of the process technology which comes from the source-drain resistance, namely Ron of the power transistor (W.-C. Chen et al., 2014). Drop-out voltage is the voltage drop across the source-drain terminal of the large power PMOS transistor as shown in Figure 1.1. The drop-out voltage becomes relatively higher compare with the supply voltage, thus impact the efficiency of LDO (Avalur & Azeemuddin, 2016; Das et al., 2017). In order to increase the efficiency of the low power LDO, there are research efforts being done to reduce the total quiescent current.

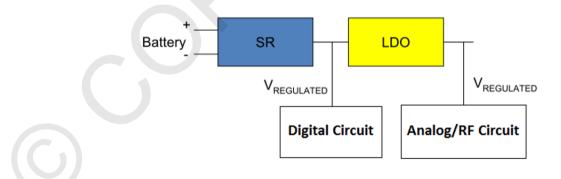

Figure 1.2: Configuration of power management unit in SoC

Figure 1.2 shows the configuration of power management unit in SoC (E. N. Y. Ho & Mok, 2011). The unregulated input supply source to the whole power management unit is normally full of noise signals. The switching regulator, such as DC/DC converter, regulates the supply source for the digital circuitry which is normally a very large circuit. The efficiency of switching regulator is usually very high and able to reach more than 98% (Y. Okuma et al., 2010). But however, switching regulator is not suitable to regulate analog or RF circuitry due to its high switching noise. As shown in Figure 1.2, the LDO input is sourced from the regulated output of switching regulator, and LDO output supplies a clean regulated output to the sensitive analog and RF circuitries. The LDO output is almost noiseless because it has gone through two stages of regulation.

#### 1.2 Motivation

From the statistical analysis, it is known that the majority operation time of most electronic devices are in idle mode (Luders et al., 2011). In order to effectively prolong the sustainability of battery life, it is critical to reduce the power consumption, especially during idle mode operation of the electronic devices (Paul et al., 2016). Analog circuits such as LDO that needs a constant drawing of current from battery will definitely contribute to the draining of battery. To be exact, LDO that regulates all analog and RF circuits are needed in large numbers, thus LDO has become the main culprit in draining the battery during devices idle mode. Hence the reduction of quiescent current in LDO is vital in today low power portable electronic devices (Kubendran et al., 2011; Saint-Laurent et al., 2015). The reduction of quiescent current could further improve the efficiency of the LDO especially during idle state, where the output loading current is zero or very small (Pathak, Hajkazemi, Tavana, Homayoun, & Savidis, 2016). Therefore, designing a low power LDO with low quiescent current is the first motivation of this research work.

Furthermore, stability compensation of SoC integrated LDO during low load current condition has always been a problematic issue. While the load current reducing to low level, the loop stability will continue worsen and probably collapse at the zero load current. More current is usually needed to sustain the stability compensation of the LDO when output load current is reducing (Z. Peng, Lv, & She, 2012). But the increased of quiescent current will worsen the efficiency. Hence another motivation in this research work is to take the challenge in designing a LDO circuit that is able to perform self-compensation by its own, depending on the amount of load current, but at the same time preventing the usage or any increment of quiescent current. To perform both challenges as above which contradict each other is indeed not a direct and easy task.

The scope of this research work mainly focus on the loop stability and the reduction of quiescent current of the LDO during its load current is very low. The limitation is it compromises on other performance of the LDO which involve higher consumption of current such as transient response and slew-rate.

#### **1.3 Problem statements**

Figure 1.3 shows the LDO design for SoC application. The voltage reference,  $V_{REF}$  is provided by a bandgap reference (BGR). However the low power environment SoC requirement with lower supply voltage which as low as 1.20V has made conventional 1.12V output voltage of BGR not viable anymore (Jang, Park, Jeong, & Cho, 2016).

Figure 1.3 shows no external off-chip capacitor.  $C_L$  represents the load capacitance. The SoC requirement have put LDO circuit design into challenge when the external off-chip capacitor which is used for stability compensation had to be removed (Raducan & Neag, 2015; Yun, Yun, & Kim, 2017).

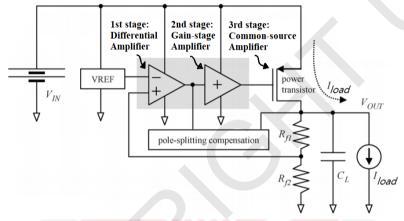

Figure 1.3: LDO design for SoC application

The LDO is viewed as a three-stage amplifier. The first stage amplifier is a differential amplifier. The second stage amplifier is a gain-stage amplifier. These two stages amplifier formed the error amplifier for the LDO. The third stage amplifier is the power PMOS transistor which is used to source high output load current. The large size of power PMOS contributes high parasitic capacitance at its gate terminal. Therefore the dominant pole for LDO in SoC application has shifted to the gate terminal of power PMOS transistor. To maintain a robust loop stability comes into challenge when the LDO needed to source a wide range of output load current from zero current to hundreds of milliampere (mA). The wide range load current has caused large variation of output impedance at LDO output node. The worst case scenario happen during zero load current where output impedance is too large and causing second pole shifted to lower frequency, hence compromise the loop stability of LDO system.

There are many reported LDO design to resolve the stability issue of SoC integrated LDO. There is a suggestion to use NMOS transistor instead of PMOS for the source follower in order to obtain low output impedance at the output of LDO (Day & Lie, 2011). This method sustain low impedance at output node over the wide range of load current and keep this pole at higher frequency. However the trade-off is that NMOS pass transistor has higher dropout voltage, thus achieving lower efficiency. There is also

another reported design imposing low-impedance at the output node of LDO (S. S. Chong & Chan, 2011). However excessive amount of current is needed in order to sustain the output in low impedance, hence resulting in higher quiescent current and worse efficiency.

Above issues have caused the low efficiency of SoC integrated LDO, especially during low load current. The efficiency equation is given in Equation (1.1) as

$$\eta = \frac{V_{out}I_{out}}{V_{in}(I_q + I_{out})} \tag{1.1}$$

, where  $I_q$  the quiescent current is and  $I_{out}$  is the output load current. From the equation, if the load current is very large comparing quiescent current, a very high efficiency can be achieved. In the other way, efficiency become worst if load current is low. By observing the total usage time of electronic devices in a day, it is known that most devices are under sleep-mode or stand-by mode most of the time. Therefore, improving efficiency at low output load current is deemed to be important in order to prolong the stand-by period of devices. Hence, reducing quiescent current during low output load current is essential.

Concluded from the above problem statements, the first issue is the conventional BGR with 1.12V voltage output is no longer viable to provide voltage reference for low power LDO. Second issue is the excessive amount of current is normally required to sustain the loop stability of LDO during low load current. These current can be reduced when load current gradually increases. The third issue is the difficulty to maintain the loop stability of LDO during very low output load current condition. Furthermore to reduce the total quiescent current of the LDO that contributed to low efficiency is another challenge to deal with, especially during low output load current condition.

#### 1.4 Research objectives

The proposed research work is carried out with the purpose of realizing quiescent current reduction of self-compensated LDO. The research objectives of this research work are:

- 1) To design a low power bandgap reference circuit with sub-1V output stage to supply a stable reference voltage for the proposed LDO.

- 2) To design a quiescent current self-reduction circuit on the proposed LDO which is able to perform current reduction during low load current.

- 3) To design a self-compensation circuit for the proposed LDO, with the capability to self-repair the worsen loop stability during low load current.

- To further reduce the total quiescent current of the proposed LDO during low load current using circuit design technique, in order to improve the efficiency of the LDO.

The circuit design of the proposed LDO is implemented using  $0.13\mu m$  CMOS process technology with 1.20V voltage supply. The proposed LDO together with bandgap reference are both fabricated into silicon chip and measurement is further conducted.

#### 1.5 Outline of the thesis

This thesis consists of six chapters. In Chapter 1, the introduction section discuss the current technology development trend and the current market demand for LDO. especially on the demand of SoC integrated LDO. The motivation of this research work has been validated. The problematic issues of LDO in SoC application is analyzed and described. And the list of research objectives for this work are being ruled out from here. Chapter 2 is the literature review chapter. Firstly, the performance parameters of LDO is being listed and explained in brief. Then the literature reviews on LDO is being discussed based on categories such as "low quiescent current LDO" review, "external capacitorless LDO" review, and "LDO with enhancement topology" review. The trade-off on the performance parameters between these research papers are discussed. Chapter 3 discusses the design consideration on the circuit design of the proposed LDO that has to be taken into concern before any design work being carried out. The process technology constraint is discussed where the characteristic and limitation of transistors used in this work is being analyzed. Then the circuit design related constraint such as headroom and power transistor design are mentioned. The correlation between the LDO output load characteristic and its frequency response is being analyzed and discussed. Transient response is mentioned in the next section. In the following section, a circuit design methodology called inversion coefficient is introduced. Then the design trade-off that has to be made in this proposed LDO design is described. In Chapter 4, a sub-1V output stage bandgap reference (BGR) design is proposed. Firstly, the BGR design methodology is discussed. They are including the matching issue, V<sub>EB</sub> of the PNP transistor, and issue pertaining BGR integration with LDO. Secondly, the principle of circuit operation is explained, then the circuit design of BGR is presented and described in subsection such as bandgap core circuit, start-up circuit, output stage circuit and opamp circuit. Thirdly, the results and discussions are presented by subsection, including PVT impact on  $V_{REF}$ , and start-up circuit. An overall conclusion is presented at the end of this chapter. In Chapter 5, a self-compensation quiescent current reduction LDO is suggested. Firstly, the design methodology is discussed. Secondly the proposed LDO's circuit operation is described. They are including error amplifier and power PMOS, low impedance circuit, and sensing and control (SAC) circuit. Thirdly, analysis on the LDO loop stability is being discussed. The stability analysis comes with two different phenomenon which are high load current phenomenon and load current below 100µA phenomenon. Fourthly, the fabrication and measurement set-up are mentioned. The layout of the proposed LDO is shown in this section. Fifthly, the results and discussions of the proposed LDO is presented, including the measurement results. They are divided into three parts which are the results of stability and self-compensation, the results of quiescent current reduction and efficiency, and the results of DC voltage performance. An overall conclusion on the LDO design is made at the end of this chapter. A final conclusion is presented in Chapter 6. The contribution and the impact of this dissertation is presented, and the future research works are mentioned in this chapter.

$\bigcirc$

#### REFERENCES

- Al-Ashmouny, K., Chang, S.-I., & Yoon, E. (2011). A 8.6 μW 3-bit programmable gain amplifier for multiplexed-input neural recording systems (pp. 2945–2948). doi:10.1109/IEMBS.2011.6090810

- Amer, A., & Sánchez-Sinencio, E. (2010). A 140mA 90nm CMOS low drop-out regulator with -56dB power supply rejection at 10MHz (pp. 1–4). doi:10.1109/CICC.2010.5617585

- Aminzadeh, H., Lotfi, R., & Mafinezhad, K. (2010). Low-dropout voltage reference: An approach to buffered architectures with low sensitivity. ISCAS 2010 - 2010 IEEE International Symposium on Circuits and Systems: Nano-Bio Circuit Fabrics and Systems, (1), 849–852. doi:10.1109/ISCAS.2010.5537428

- Aminzadeh, H., & Serdijn, W. (2011). Low-dropout regulators: Hybrid-cascode compensation to improve stability in nano-scale CMOS technologies. *Proceedings IEEE International Symposium on Circuits and Systems*, 2293–2296. doi:10.1109/ISCAS.2011.5938060

- Avalur, K. K. G., & Azeemuddin, S. (2016). System Efficiency Improvement Technique for Automotive Power Management IC Using Maximum Load Current Selector Circuit. Proceedings of the IEEE International Conference on VLSI Design, 2016– March, 240–245. doi:10.1109/VLSID.2016.56

- Bai, Y., & Lin, C. (2015). Using a Hybrid LDO Regulator and a Switching Regulator Circuit to Reduce the Power Consumption in the Light Load Operation of a Server Motherboard.

- Bautista, M. G., Jilluh, Q. I., Heimlich, M., Dutkiewicz, E., & Pasco, J. (2015). Design of Low Power, High PSRR Low Drop-Out Voltage Regulator, (December).

- Binkley, D. M. (n.d.). *The Analog CMOS Design, Tradeoffs and Optimization Spreadsheet. Tradeoffs and Optimization in Analog CMOS Design.*

- Bu, S., Guo, J., & Leung, K. N. (2017). A 200-ps-Response-Time Output-Capacitorless Low-Dropout Regulator with Unity-Gain Bandwidth >100 MHz in 130-nm CMOS. *IEEE Transactions on Power Electronics*, 8993(c), 1–1. doi:10.1109/TPEL.2017.2711017

- Chen, C.-M., & Hung, C.-C. (2011). A fast self-reacting capacitor-less low-dropout regulator (pp. 375–378). doi:10.1109/ESSCIRC.2011.6044985

- Chen, L. M., Yu, Z. H., Chen, C. Y., Hu, X. Y., Fan, J., Yang, J., & Hei, Y. (2015). A 1-V, 1.2-mA fully integrated SoC for digital hearing aids. *Microelectronics Journal*, 46(1), 12–19. doi:10.1016/j.mejo.2014.09.013

- Chen, W.-C., Ping, S.-Y., Huang, T.-C., Lee, Y.-H., Chen, K.-H., & Wey, C.-L. (2014). A Switchable Digital #x2013;Analog Low-Dropout Regulator for Analog Dynamic Voltage Scaling Technique. *IEEE Journal of Solid-State Circuits*, 49(3), 740–750. doi:10.1109/JSSC.2013.2297395

- Chen, W.-M., Chiueh, H., Chen, T.-J., Ho, C.-L., Jeng, C., Ker, M.-D., ... Wu, C.-Y. (2014). A Fully Integrated 8-Channel Closed-Loop Neural-Prosthetic CMOS SoC for Real-Time Epileptic Seizure Control. *IEEE Journal of Solid-State Circuits*, 49(1), 232–247. doi:10.1109/JSSC.2013.2284346

- Chong, S., & Chan, P. K. (2013). A 0.9-/spl mu/A Quiescent Current Output-Capacitorless LDO Regulator With Adaptive Power Transistors in 65-nm CMOS. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 60(4), 1072–1081. doi:10.1109/TCSI.2012.2215392

- Chong, S. S., & Chan, P. K. (2011). A quiescent power-aware low-voltage output capacitorless low dropout regulator for SoC applications (pp. 37–40). doi:10.1109/ISCAS.2011.5937495

- Cmos, L. (2011). Bandgap Reference With a Low Dropout or Source Follower Mode, 19(7), 1305–1309.

- Cui, L. (2011). Design of a high precision bandgap voltage reference. Proceedings of 2011 International Conference on Electronic & Mechanical Engineering and Information Technology, 4(1), 2187–2190. doi:10.1109/EMEIT.2011.6023473

- Darwish, M., Mohsen, M., Saad, A., & Weldon, J. A. (2016). Ultralow-Area Hysteretic Control LDO with Sub-1-µA Quiescent Current. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 63(10), 1004–1008. doi:10.1109/TCSII.2016.2536240

- Das, D., Maity, S., Nasir, S. Bin, Ghosh, S., Raychowdhury, A., & Sen, S. (2017). High efficiency power side-channel attack immunity using noise injection in attenuated signature domain. Proceedings of the 2017 IEEE International Symposium on Hardware Oriented Security and Trust, HOST 2017, 62–67. doi:10.1109/HST.2017.7951799

- Day, J., & Lie, D. Y. C. (2011). An output-capacitorless linear regulator for integrated portable power solutions (pp. 1–4). doi:10.1109/MWSCAS.2011.6026366

- de Oliveira Dutra, O., & Pimenta, T. C. (2012). A low power low noise OTA with adjustable gain PID feedback network (pp. 403–406). doi:10.1109/MIEL.2012.6222887

- Duwe, M., & Chen, T. (2012). Offset correction of low power, high precision op amp using digital assist for biomedical applications (pp. 850–853). doi:10.1109/ISCAS.2012.6272175

- El-Nozahi, M., Amer, A., Torres, J., Entesari, K., & Sanchez-Sinencio, E. (2010). High PSR Low Drop-Out Regulator With Feed-Forward Ripple Cancellation Technique. *IEEE Journal of Solid-State Circuits*, 45(3), 565–577. doi:10.1109/JSSC.2009.2039685

- Elzeftawi, M., & Theogarajan, L. (2013). A 10pJ/bit 135Mbps IR-UWB transmitter using pulse position modulation and with on-chip LDO regulator in 0.13 #x00B5;m CMOS for biomedical implants (pp. 37–39). doi:10.1109/BioWireleSS.2013.6613667

- Gjanci, J., & Chowdhury, M. H. (2011). A hybrid scheme for on-chip voltage regulation in system-on-a-chip (SOC). *IEEE Transactions on Very Large Scale Integration* (VLSI) Systems, 19(11), 1949–1959. doi:10.1109/TVLSI.2010.2072997

- Goldstein, B., Kim, D., Xu, J., Vanderlick, T. K., & Culurciello, E. (2012). CMOS Low Current Measurement System for Biomedical Applications. *IEEE Transactions on Biomedical Circuits and Systems*, 6(2), 111–119. doi:10.1109/TBCAS.2011.2182512

- Guo, J., & Leung, K. N. (2013). A 25mA CMOS LDO with #x2212;85dB PSRR at 2.5MHz (pp. 381–384). doi:10.1109/ASSCC.2013.6691062

- Gupta, H., Mishra, G. K., Nidhi, Rizvi, I., & Yadav, A. K. (2016). A capacitor-less low drop-out voltage regulator for SoC applications. *International Conference on Electrical, Electronics, and Optimization Techniques, ICEEOT 2016*, (2), 4203– 4208. doi:10.1109/ICEEOT.2016.7755509

- Haibi, H., Akita, I., & Ishida, M. (2013). A 27-nV/ #x221A;Hz 0.015-mm2 three-stage operational amplifier with split active-feedback compensation (pp. 365–368). doi:10.1109/ASSCC.2013.6691058

- Hinojo, J., Luján-Martínez, C., & Torralba, A. (2014). LDO compensation with variable Miller series resistance. *Electronics Letters*, 50(3), 159–161. doi:10.1049/el.2013.3450

- Ho, E. N. Y., & Mok, P. K. T. (2010). A capacitor-less CMOS active feedback lowdropout regulator with slew-rate enhancement for portable on-chip application. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 57(2), 80–84. doi:10.1109/TCSII.2009.2038630

- Ho, E. N. Y., & Mok, P. K. T. (2011). Design optimization of an output capacitor-less low dropout regulator with compensation capcitance reduction and slew-rate enhancement technique. *Proceedings - IEEE International Symposium on Circuits* and Systems, 53–56. doi:10.1109/ISCAS.2011.5937499

- Ho, M., Leung, K.-N., & Mak, K.-L. (2010). A Low-Power Fast-Transient 90-nm Low-Dropout Regulator With Multiple Small-Gain Stages. *IEEE Journal of Solid-State Circuits*, 45(11), 2466–2475. doi:10.1109/JSSC.2010.2072611

- Ho, M., & Leung, K. N. (2011). Dynamic bias-current boosting technique for ultralowpower low-dropout regulator in biomedical applications. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 58(3), 174–178. doi:10.1109/TCSII.2011.2110330

- Hong, S. W., & Cho, G. H. (2016). High-Gain Wide-Bandwidth Capacitor-Less Low-Dropout Regulator (LDO) for Mobile Applications Utilizing Frequency Response of Multiple Feedback Loops. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 63(1), 46–57. doi:10.1109/TCSI.2015.2512702

- Hsieh, C.-H., Du, C.-Y., & Lee, S.-Y. (2014). Power management with energy harvesting from a headphone jack (pp. 1989–1992). doi:10.1109/ISCAS.2014.6865553

- Ivanov, V., Brederlow, R., & Gerber, J. (2012). An ultra low power bandgap operational at supply from 0.75 v. *IEEE Journal of Solid-State Circuits*, 47(7), 1515–1523. doi:10.1109/JSSC.2012.2191192

- Jalalifar, M., & Byun, G.-S. (2013). An ultra-low power spike detector for implantable biomedical systems (pp. 1–4). doi:10.1109/WAMICON.2013.6572752

- Jang, Y. M., Park, C. H., Jeong, J. S., & Cho, S. B. (2016). Design of a sub-1-V bandgap reference for low dropout regulator in SR-ALF-VCOs. ISOCC 2015 -International SoC Design Conference: SoC for Internet of Everything (IoE), 237– 238. doi:10.1109/ISOCC.2015.7401735

- Keikhosravy, K., & Mirabbasi, S. (2014). Regulator Using Bulk-Modulation Technique, *61*(11), 3105–3114.

- Kim, Y.-I., & Lee, S.-S. (2012). Fast transient capacitor-less LDO regulator using lowpower output voltage detector. *Electronics Letters*, 48(3), 175–177. doi:10.1049/el.2011.3671

- Kim, Y., & Lee, S. (2013). A Capacitorless LDO Regulator With Fast Feedback Technique and Low-Quiescent Current Error Amplifier. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 60(6), 326–330. doi:10.1109/TCSII.2013.2258250

- Koay, K. C., & Chan, P. K. (2017). A Low Energy-Noise 65nm CMOS Switched-Capacitor Resistive-Bridge Sensor Interface. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 64(4), 799–810. doi:10.1109/TCSI.2016.2625310

- Kok, C.-L., Huang, Q., Zhu, D., Siek, L., & Lim, W. M. (2012). A fully digital green LDO regulator dedicated for biomedical implant using a power-aware binary switching technique (pp. 5–8). doi:10.1109/APCCAS.2012.6418957

- Koushaeian, L., & Skafidas, S. (2010). A 65nm CMOS low-power, low-voltage bandgap reference with using self-biased composite cascode opamp. Low-Power Electronics and Design (ISLPED), 2010 ACM/IEEE International Symposium on, 95–98. doi:10.1145/1840845.1840866

- Kubendran, R., Krishnan, H., Manola, B., John, S. W. M., Chappell, W. J., & Irazoqui, P. P. (2011). A generic miniature multi-feature programmable wireless powering headstage ASIC for implantable biomedical systems (pp. 5617–5620). doi:10.1109/IEMBS.2011.6091359

- Lee, K. Y., Abbasizadeh, H., & Hayder, A. S. (2016). Highly accurate capacitor-free LDO with sub-1 V –120 dB PSRR bandgap voltage reference. *Electronics Letters*, 52(15), 1323–1325. doi:10.1049/el.2016.0193

- Lee, S.-Y., Yang, C.-M., Hsieh, C.-H., & Fang, J. Q. (2010). A wireless front-end for implantable cardiac micro-stimulator (pp. 438–441). doi:10.1109/APCCAS.2010.5774844

- Lee, Y. J., Qu, W., Singh, S., Kim, D. Y., Kim, K. H., Kim, S. H., ... Cho, G. H. (2017). A 200-mA Digital Low Drop-Out Regulator With Coarse-Fine Dual Loop in Mobile Application Processor. *IEEE Journal of Solid-State Circuits*, 52(1), 64–76. doi:10.1109/JSSC.2016.2614308

- Lepkowski, W., Wilk, S. J., Ghajar, M. R., Bakkaloglu, B., & Thornton, T. J. (2012). An integrated MESFET voltage follower LDO for high power and PSR RF and analog applications. *Proceedings of the Custom Integrated Circuits Conference*, (V), 8–11. doi:10.1109/CICC.2012.6330634

- Leung, K. N., & Ng, Y. S. (2010). A CMOS Low-Dropout Regulator With a Momentarily Current-Boosting Voltage Buffer. *IEEE Transactions on Circuits* and Systems I: Regular Papers, 57(9), 2312–2319. doi:10.1109/TCSI.2010.2043171

- Li, G., Guo, J., Zheng, Y., Huang, M., & Chen, D. (2016). Cascoded flipped voltage follower based output-capacitorless low-dropout regulator for SoCs. *International System on Chip Conference*, 2016–Febru(c), 368–373. doi:10.1109/SOCC.2015.7406985

- Lim, Y., Member, S., Lee, J., Member, S., Lee, Y., Member, S., ... Choi, J. (2017). An External Capacitor-Less Ultralow-Dropout Regulator Using a Loop-Gain Stabilizing Technique for High Power-Supply Rejection Over a Wide Range of Load Current, 25(11), 3006–3018.

- Lo, Y. L., & Chen, W. J. (2012). A 0.7 v input output-capacitor-free digitally controlled low-dropout regulator with high current efficiency in 0.35 µm CMOS technology. *Microelectronics Journal*, 43(11), 756–765. doi:10.1016/j.mejo.2012.07.008

- Lotfi Navaii, M., Jalali, M., & Sadjedi, H. (2012). An ultra-low power RF interface for wireless-implantable microsystems. *Microelectronics Journal*, 43(11), 848–856. doi:10.1016/j.mejo.2012.06.006

- Lovaraju, C., Maity, A., & Patra, A. (2013). A Capacitor-less Low Drop-out (LDO) Regulator with Improved Transient Response for System-on-Chip Applications (pp. 130–135). doi:10.1109/VLSID.2013.176

- Luders, M., Eversmann, B., Gerber, J., Huber, K., Kuhn, R., Schmitt-Landsiedel, D., & Brederlow, R. (2011). A fully-integrated system power aware LDO for energy harvesting applications (pp. 244–245). Retrieved from http://ezproxy.upm.edu.my:2078/ielx5/5976946/5985982/05986129.pdf?tp=&arn umber=5986129&isnumber=5985982

- Lueders, M., Eversmann, B., Gerber, J., Huber, K., Kuhn, R., Zwerg, M., ... Brederlow, R. (2013). Architectural and Circuit Design Techniques for Power Management of Ultra-Low-Power MCU Systems. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems, Early Access Online*. doi:10.1109/TVLSI.2013.2290083

- Márquez, A., Calvo, B., Member, I., Medrano, N., Member, I., & Circuit, A. L. D. O. C. (2017). A Power Efficient LDO Regulator for Portable CMOS SoC Measurement Systems, 06, 3–8.

- Mart, A. (2013). A bandgap voltage reference in 0 . 18 µ m CMOS technology, 97–100. doi:10.1109/MWSCAS.2013.6674594

- Mazumdar, K., Bartling, S., Khanna, S., & Stan, M. (2015). A digitally-controlled power-aware low-dropout regulator to reduce standby current drain in ultra-lowpower MCU. *Proceedings - International Symposium on Quality Electronic Design, ISQED, 2015–April,* 98–102. doi:10.1109/ISQED.2015.7085406

- Ming, X., Li, Q., Zhou, Z., & Zhang, B. (2012). An Ultrafast Adaptively Biased Capacitorless LDO With Dynamic Charging Control. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 59(1), 40–44. doi:10.1109/TCSII.2011.2177698

- Ming, X., Ma, Y. Q., Zhou, Z. K., & Zhang, B. (2010). A high-precision compensated CMOS bandgap voltage reference without resistors. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 57(10), 767–771. doi:10.1109/TCSII.2010.2067770

- Narasimhan, S., Chiel, H. J., & Bhunia, S. (2011). Ultra-low-power and robust digitalsignal-processing hardware for implantable neural interface microsystems. *IEEE Transactions on Biomedical Circuits and Systems*, 5(2), 169–178. doi:10.1109/TBCAS.2010.2076281

- Nasrollahpour, M., Hamedi-Hagh, S., Bastan, Y., & Amiri, P. (2017). ECP technique based capacitor-less LDO with high PSRR at low frequencies, -89dB PSRR at 1MHz and enhanced transient response. SMACD 2017 - 14th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design, 7–10. doi:10.1109/SMACD.2017.7981570

- Navarro, J., & Ishibe, E. (2011). A simple CMOS bandgap reference circuit with sub-1-V operation. Proceedings - IEEE International Symposium on Circuits and Systems, 2, 2289–2292. doi:10.1109/ISCAS.2011.5938059

- Ng, D. C. W., Kwong, D. K. K., & Wong, N. (2011). A sub-1 V, 26 μw, low-outputimpedance CMOS bandgap reference with a low dropout or source follower mode. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 19(7), 1305– 1309. doi:10.1109/TVLSI.2010.2046658

- Okuma, Y., Ishida, K., Ryu, Y., Zhang, X., Chen, P.-H., Watanabe, K., ... Sakurai, T. (2010). 0.5-V input digital LDO with 98.7% current efficiency and 2.7- #x00B5;A quiescent current in 65nm CMOS (pp. 1–4). doi:10.1109/CICC.2010.5617586

- Okuma, Y., Ishida, K., Ryu, Y., Zhang, X., Chen, P., Watanabe, K., ... Sakurai, T. (2010). 0.5-V Input Digital LDO with 98. 7 % Current Efficiency and 2. 7-μA Quiescent Current in 65nm CMOS, 98–101. doi:10.1109/CICC.2010.5617586

- Park, C.-J., Onabajo, M., & Silva-Martinez, J. (2014). External Capacitor-Less Low Drop-Out Regulator With 25 dB Superior Power Supply Rejection in the 0.4 #x2013;4 MHz Range. *IEEE Journal of Solid-State Circuits*, 49(2), 486–501. doi:10.1109/JSSC.2013.2289897

- Park, Y., & Salman, E. (2016). On-chip hybrid regulator topology for portable SoCs with near-threshold operation. *Proceedings - IEEE International Symposium on Circuits and Systems*, 2016–July, 786–789. doi:10.1109/ISCAS.2016.7527358

- Pathak, D., Hajkazemi, M. H., Tavana, M. K., Homayoun, H., & Savidis, I. (2016). Energy efficient on-chip power delivery with run-time voltage regulator clustering. *Proceedings - IEEE International Symposium on Circuits and Systems*, 2016–July, 1210–1213. doi:10.1109/ISCAS.2016.7527464

- Paul, A., Park, S. P., Somasekhar, D., Kim, Y. M., Borkar, N., Karpuzcu, U. R., & Kim, C. H. (2016). System-Level Power Analysis of a Multicore Multipower Domain Processor with ON-Chip Voltage Regulators. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, 24(12), 3468–3476. doi:10.1109/TVLSI.2016.2555954

- Peng, S. Y., Liu, L. H., Chang, P. K., Wang, T. Y., & Li, H. Y. (2017). A Power-Efficient Reconfigurable Output-Capacitor-Less Low-Drop-Out Regulator for Low-Power Analog Sensing Front-End. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 64(6), 1318–1327. doi:10.1109/TCSI.2016.2561638

- Peng, Z., Lv, C., & She, S. (2012). Design of a dynamic frequency compensation low dropout voltage regulator with buffer impedance attenuation (pp. 2521–2524). doi:10.1109/CECNet.2012.6201453

- Raducan, C., & Neag, M. (2015). Capacitorless LDO with fast transient response based on a high slew-rate error amplifier. *Proceedings of the International Semiconductor Conference, CAS, 2015–Decem, 285–288.* doi:10.1109/SMICND.2015.7355234

- Ramos, J., Ausin, J. L., Duque-Carrillo, J. F., & Torelli, G. (2011). Design considerations on CMOS limiting amplifiers for wearable biomedical systems (pp. 294–297). doi:10.1109/ECCTD.2011.6043344

- Ramzan, R., Member, S., Zafar, F., & Member, S. (2014). High Efficiency Fully CMOS VCO Rectifier for μ Watt Resonant Wireless Power Transfer, 7747(Table 1), 134– 138. doi:10.1109/TCSII.2014.2386262

- Rashid, M. W. (2010). Reverse Nested Miller Compensation Using Current Buffers in a Three Stage Low Drop-out Voltage Regulator, 57(May), 250–254.

- Ru, B. (2010). Design of a low-power bandgap current reference. 2010 International Conference on E-Product E-Service and E-Entertainment, ICEEE2010, 10–12. doi:10.1109/ICEEE.2010.5661273

- Saberkari, A., Alarcon, E., & Shokouhi, S. B. (2012). CMOS fast transient low-dropout regulator (pp. 105–108). doi:10.1109/IranianCEE.2012.6292333

- Saint-Laurent, M., Bassett, P., Lin, K., Mohammad, B., Wang, Y., Chen, X., ... Anderson, W. (2015). A 28 nm DSP Powered by an On-Chip LDO for High-Performance and Energy-Efficient Mobile Applications. *IEEE Journal of Solid-State Circuits*, 50(1), 81–91. doi:10.1109/JSSC.2014.2371454

- Shirmohammadli, V., & Saberkari, A. (2017). Low Power Output-Capacitorless Class-AB CMOS LDO Regulator, 2–5.

- Sun, N., & Sobot, R. (n.d.). A LOW POWER LOW VOLTAGE BANDGAP REFERENCE IN CMOS Na Sun and Robert Sobot Department of Electrical and Computer Engineering The University of Western Ontario London ON, Canada N6A 5B9, 3(1).

- Suriyavejwongs, P., Supmonchai, B., & Opasjumruskit, K. (2015). Slew-rate enhanced capacitor-less low drop-out regulator with on-the-fly adjustable output voltage. *Proceedings of the 2015 IEEE International Conference on Electron Devices and Solid-State Circuits, EDSSC 2015*, 186–189. doi:10.1109/EDSSC.2015.7285081

- Talewad, D., Nandi, A. V., & Vaishail, B. M. (2016). Design and implementation of BiCMOS based low temperature coefficient bandgap reference using 130nm technology. NUICONE 2015 - 5th Nirma University International Conference on Engineering, 0–5. doi:10.1109/NUICONE.2015.7449637

- Tan, X. L., Koay, K. C., Chong, S. S., & Chan, P. K. (2014). A FVF LDO Regulator With Dual-Summed Miller Frequency Compensation for Wide Load Capacitance Range Applications. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 61(5), 1304–1312. doi:10.1109/TCSI.2014.2309902

- Transient-enhanced, A. C. I., Oh, T., & Hwang, I. (2014). Current Efficiency at 80-mA Load, 1281–1286.

- Vaisband, I., Member, S., & Friedman, E. G. (2015). Stability of Distributed Power Delivery Systems with Multiple Parallel On-Chip LDO Regulators, 8993(c), 5625–5634. doi:10.1109/TPEL.2015.2493512

- Valapala, H., & Furth, P. M. (2012). Analysis and design of fully integrated very low quiescent current LDOs (pp. 230–233). doi:10.1109/MWSCAS.2012.6291999

- Verrascina, N., Begueret, J. B., & Borgarino, M. (2016). An ULP and very efficient adaptively biased LDO regulator for harvesting application. 14th IEEE International NEWCAS Conference, NEWCAS 2016, (1), 1–4. doi:10.1109/NEWCAS.2016.7604765

- Wang, L., Mao, W., Wu, C., Chang, A., & Lian, Y. (2017). A fast transient LDO based on dual loop FVF with high PSRR. 2016 IEEE Asia Pacific Conference on Circuits and Systems, APCCAS 2016, 99–102. doi:10.1109/APCCAS.2016.7803906

- Wang, L. Y., Li, B., & Wu, Z. H. (2012). A low-power CMOS power amplifier for implanted biomedical ultra wideband (UWB) applications (pp. 1–3). doi:10.1109/ICSICT.2012.6467614

- Wu, Q., Li, W., Li, N., & Ren, J. (2011). A 1.2 V 70 mA low drop-out voltage regulator in 0.13μm CMOS process (pp. 978–981). doi:10.1109/ASICON.2011.6157370

- Xiaoyun, T., Chen, L., Min, S., & Guanshi, W. (2011). A low temperature coefficient 4th-order curvature-compensated CMOS bandgap reference. 2011 Academic International Symposium on Optoelectronics and Microelectronics Technology, AISOMT 2011, 251–254. doi:10.1109/AISMOT.2011.6159366

- Yoon, K. S., Kim, H. S., Qu, W., Yuk, Y. S., & Cho, G. H. (2018). Fully Integrated Digitally Assisted Low-Dropout Regulator for a NAND Flash Memory System. *IEEE Transactions on Power Electronics*, 33(1), 388–406. doi:10.1109/TPEL.2017.2665476

- Yun, S. J., Yun, J. S., & Kim, Y. S. (2017). Capless LDO Regulator Achieving -76 dB PSR and 96.3 fs FOM. *IEEE Transactions on Circuits and Systems II: Express Briefs*, 64(10), 1147–1151. doi:10.1109/TCSII.2016.2628965

- Zarate-Roldan, J., Carreon-Bautista, S., Costilla-Reyes, A., & Sanchez-Sinencio, E. (2015). A power management unit with 40 dB switching-noise-suppression for a thermal harvesting array. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 62(8), 1918–1928. doi:10.1109/TCSI.2015.2434099

- Zarate-Roldan, J., Wang, M., Torres, J., & Sanchez-Sinencio, E. (2016). A Capacitor-Less LDO with High-Frequency PSR Suitable for a Wide Range of On-Chip Capacitive Loads. *IEEE Transactions on Very Large Scale Integration (VLSI)* Systems, 24(9), 2970–2982. doi:10.1109/TVLSI.2016.2527681

- Zeng, Y., & Tan, H. Z. (2016). A FVF based LDO with dynamic bias current for low power RFID chips. 2016 IEEE International Conference on RFID Technology and Applications, RFID-TA 2016, 61–64. doi:10.1109/RFID-TA.2016.7750736

- Zhao, C., & Huang, J. (2011). A new high performance bandgap reference. 2011 International Conference on Electronics, Communications and Control (ICECC), (21611514), 64–66. doi:10.1109/ICECC.2011.6067602

- Zou, L., & Larsen, T. (2011). Dynamic power control circuit for implantable biomedical devices. *IET Circuits, Devices Systems*, 5(4), 297–302. doi:10.1049/ietcds.2010.0330