# **UNIVERSITI PUTRA MALAYSIA**

# RADIO FREQUENCY FRONT END RECEIVER BLOCKS WITH ULTRA LOW SUPPLY VOLTAGE AND LOW POWER DISSIPATION FOR ZIGBEE APPLICATIONS

**TAN GIM HENG**

FK 2015 167

# RADIO FREQUENCY FRONT END RECEIVER BLOCKS WITH ULTRA LOW SUPPLY VOLTAGE AND LOW POWER DISSIPATION FOR ZIGBEE APPLICATIONS

By TAN GIM HENG

Thesis Submitted to the School of Graduate Studies, Universiti Putra Malaysia, in Fulfillment of the Requirements for the Degree of Doctor of Philosophy

# **COPYRIGHT**

All material contained within the thesis, including without limitation text, logos, icons, photographs and all other artwork, is copyright material of Universiti Putra Malaysia unless otherwise stated. Use may be made of any material contained within the thesis for non-commercial purposes from the copyright holder. Commercial use of material may only be made with the express, prior, written permission of Universiti Putra Malaysia.

Copyright © Universiti Putra Malaysia

Abstract of thesis presented to the Senate of Universiti Putra Malaysia in fulfilment of the requirement for the degree of Doctor of Philosophy

# RADIO FREQUENCY FRONT END RECEIVER BLOCKS WITH ULTRA LOW SUPPLY VOLTAGE AND LOW POWER DISSIPATION FOR ZIGBEE APPLICATIONS

By

#### TAN GIM HENG

**April 2015**

Chair: Roslina Mohd Sidek, PhD

Faculty: Engineering

Portable wireless devices have been the heat of demands in recent years for many applications such as Wireless Sensor Network (WSN) which requires low power consumption since these devices are commonly powered up by battery. One way to reduce circuit power consumption is to lower the supply voltage or DC current of the circuit. Continuous modern technology scaling with a proportional supply voltage reduction outlays a challenge in designing Radio Frequency (RF) circuits. In fact, the recent supply voltage and power consumption for mixer have been saturated at around 0.8V and 1mW respectively.

Direct conversion receiver (DCR) is the preferred choice of low power adaptation for the receiver front-end. The most common topologies for mixer are Gilbert cell, folded cascode and current bleeding mixer. However, these architectures still require high supply voltage to operate. The proposed architecture combines the current bleeding technique and folded structure to realize the operation at ultra-low supply voltage of 0.5V while enhancing the isolation between Local Oscillator (LO) and RF ports. This mixer exhibits a measured conversion gain of 11dB at the radio frequency (RF) of 2.4GHz, an input third-order intercept point (IIP3) of -0.4dBm and a LO-RF isolation measured to 60 dB and the DC power consumption is 850µW.

This research also includes the design and analysis of current bleeding mixer topology adapting forward body bias technique coupled with the integration of an inductor at the gate of the NMOS bleeding transistor to increase the conversion gain without additional DC power consumption. The measured conversion gain and IIP3 of this mixer is 13dB and -0.5dBm respectively and only consume DC power of  $480\mu w$  and operates at 0.35V of supply voltage. Integrated LNA-Mixer is investigated in this thesis which focuses on ultra-low voltage and low power implementation. This integrated chip features a simulated conversion gain of 20.3dB at the radio frequency (RF) of 2.4GHz, an input third-order intercept point (IIP3) of -10.3dBm and Noise Figure (NF) is at 7.2dB. The dc power consumption is 950 $\mu w$  while working at the supply voltage of 0.5V.

The circuits are designed such that the critical transistors operate at optimum transconductance to meet the low power requirement of ZigBee applications. All circuits were fabricated using CMOS 0.13um technology and measurement was

performed on die samples. As a conclusion, the ultra-low voltage and low-power techniques used in this research meets the requirement for ZigBee applications while working at supply voltage of 0.5V and 0.35V with power dissipation of less than 1mW.

# Abstrak tesis yang dikemukakan kepada Senat Universiti Putra Malaysia sebagai memenuhi keperluan untuk ijazah Doktor Falsafah

# BLOK PENERIMA BAHAGIAN DEPAN FREKUENSI RADIO DENGAN VOLTAN BEKALAN ULTRA RENDAH DAN PELEPASAN KUASA RENDAH UNTUK APLIKASI ZIGBEE

Oleh

#### TAN GIM HENG

**April 2015**

Pengerusi: Roslina Mohd Sidek, PhD Fakulti: Fakulti Kejuruteraan

Permintaan peranti wayarles mudah alih meningkat kebelakangan ini untuk berbagai aplikasi seperti Rangkaian Sensor Tanpa Wayar (WSN) yang memerlukan penggunaan kuasa yang rendah kerana ianya bergantung kepada bateri. Satu cara untuk mengurangkan penggunaan kuasa litar adalah dengan mengurangkan voltan bekalan atau arus pincangan. Penskalaan teknologi modern yang berterusan berkadar dengan pengurangan voltan memberi cabaran dalam mereka bentuk litar frekuensi radio (RF). Malah, baru-baru ini, voltan bekalan dan penggunaan kuasa untuk pencampur telah masing-masing tepu pada kira-kira 0.8V dan 1mW.

Penerima Penukaran Langsung (DCR) adalah pilihan yang lebih sesuai untuk adaptasi kuasa rendah bagi penerima bahagian depan. Topologi yang biasa digunakan untuk pencampur adalah sel Gilbert, kaskod berlipat dan pencampur penyaliran arus. Walau bagaimanapun, kerangka ini masih memerlukan voltan bekalan yang tinggi untuk beroperasi. Seni bina yang dicadangkan ialah dengan menggunakan gabungan teknik penyaliran arus dan struktur berlipat untuk merealisasikan operasi pada voltan bekalan ultra-rendah di samping meningkatkan pengasingan antara pelabuhan pengayun tempatan (LO) dan RF. Pencampur ini mempamerkan gandaan penukaran yang diukur pada 11dB pada frekuensi radio (RF) 2.4GHz, satu titik input ketiga-perintah memintas (IIP3) pada -0.4dBm, pengasingan LO-RF yang diukur pada 60dB dan penggunaan kuasa DC adalah 850µW.

Tesis ini juga melaporkan reka bentuk dan analisis topologi pencampur arus penyaliran ultra kuasa rendah dan voltan rendah dengan menggunakan teknik pincangan substrat kehadapan dengan integrasi induktor di get transistor penyaliran untuk meningkat gandaan penukaran tanpa penambahan DC kuasa. Gandaan penukaran dan IIP3 pencampur adalah masing-masing 13dB dan -0.5dBm masing-masing dan hanya menggunakan kuasa DC 480µw dan beroperasi pada 0.35V voltan bekalan. LNA-pencampur bersepadu dikaji dalam tesis ini dengan memberi tumpuan kepada voltan ultra rendah dan pelaksanaan kuasa yang rendah. Pencampur bersepadu ini mempunyai gandaan penukaran 20.3dB pada frekuensi radio (RF), 2.4GHz, satu titik input ketigaperintah memintas (IIP3) pada -10.3dBm dan angka hingar (NF) adalah di 7.2dB. Penggunaan kuasa DC adalah 950µw dengan voltan bekalan 0.5V.

Litar direka bentuk dengan memastikan transitor yang kritikal beroperasi pada transkonduktans yang optimun bagi memenuhi keperluan kuasa rendah applikasi ZigBee. Semua litar yang direka bentuk dengan menggunakan teknologi CMOS 0.13um dan pengukuran dilakukan terus pada sampel die. Kesimpulannya, voltan dan kuasa rendah teknik yang digunakan dalam reka bentuk memenuhi keperluan untuk permohonan ZigBee dan boleh beroperasi pada voltan bekalan 0.5V dan 0.35V dengan kuasa pelepasan kurang dari 1mW.

#### **ACKNOWLEDGEMENTS**

The completion of my thesis was made possible with the help rendered by many people. First and foremost, I would like to express my sincere gratitude and heartfelt appreciation to my supervisor, Associate Professor Dr. Roslina Mohd Sidek, for her invaluable advices, technical guidance, great patience and continuous inspiration. She always encourages all her students to have high aspiration and strive for excellence. I would also like to thank my co-supervisor, Dr.Maryam Mohd Isa and Dr. Harikrishnan Ramiah for their excellent advice and constructive suggestions in helping to shape my project.

In addition, I would like to thank my research group members who have been working with me during my PhD studies. They are Chong Wei Keat, Nadini and Lioe De Xing. Besides sharing their academic knowledge and technical skills, they have provided good co-operation to me in my lab work. I am also grateful to all my close friends, for their encouragement in times of need. I want to extend my sincere thanks to all my friends in the Laboratory of IC Design for moral support and excellent work atmosphere. Besides, I would like to thank my family, my wife, Low Xun Yun and my daughter, Sophie Tan Wei Zhi who always encouraged me in pursuing my studies. Finally, thanks to all those who contributed in one way or another to the success of this research.

This thesis was submitted to the Senate of Universiti Putra Malaysia and has been accepted as fulfilment of the requirement for the degree of Doctor of Philosophy. The members of the Supervisory Committee were as follows:

# Roslina Mohd Sidek, PhD

Associate Professor Faculty of Engineering Universiti Putra Malaysia (Chairman)

# Maryam Mohd Isa, PhD

Senior Lecturer Faculty of Engineering Universiti Putra Malaysia (Member)

# Harikrishnan Ramiah, PhD

Senior Lecturer Faculty of Engineering University of Malaya (Member)

# **BUJANG BIN KIM HUAT, PhD**

Professor and Dean School of Graduate Studies Universiti Putra Malaysia

Date:

#### **Declaration by graduate student**

- I hereby confirm that: this thesis is my original work;

- quotations, illustrations and citations have been duly referenced;

- this thesis has not been submitted previously or concurrently for any other degree at any other institutions;

- intellectual property from the thesis and copyright of thesis are fully-owned by Universiti Putra Malaysia, as according to the Universiti Putra Malaysia (Research) Rules 2012; written permission must be obtained from supervisor and the office of Deputy Vice-Chancellor (Research and Innovation) before thesis is published (in the form of written, printed or in electronic form) including books, journals, modules, proceedings, popular writings, seminar papers, manuscripts, posters, reports, lecture notes, learning modules or any other materials as

- there is no plagiarism or data falsification/fabrication in the thesis, and scholarly integrity is upheld as according to the Universiti Putra Malaysia (Graduate Studies) Rules 2003 (Revision 2012-2013) and the Universiti Putra Malaysia (Research) Rules 2012. The thesis has undergone plagiarism detection software.

| Signature: | Date:                           |

|------------|---------------------------------|

| -          | atric No.: Tan Gim Heng GS24572 |

stated in the Universiti Putra Malaysia (Research) Rules 2012;

# **Declaration by Members of Supervisory Committee**

This is to confirm that:

- the research conducted and the writing of this thesis was under our supervision;

- supervision responsibilities as stated in the Universiti Putra Malaysia (Graduate Studies) Rules 2003 (Revision 2012-2013) are adhered to.

Signature: \_\_\_\_\_\_ Signature: \_\_\_\_\_\_ Name of Name of Chairman of Member of Supervisory Supervisory

Committee: ROSLINA MOHD SIDEK Committee: MARYAM MOHD ISA

Signature:

Name of Member of Supervisory

Committee: HARIKRISHNAN RAMIAH

# TABLE OF CONTENTS

| ABS<br>ACS<br>API<br>DEG<br>LIS<br>LIS | PROV<br>CLAR<br>T OF<br>T OF                  | K<br>WLEDGEMENTS                                                                                                                                                    | Page i iii v vi viii xiii xiv xvi |

|----------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| СН                                     | APTE                                          |                                                                                                                                                                     |                                   |

| 1                                      | INT<br>1.1                                    | RODUCTION  Motivation                                                                                                                                               | 1                                 |

|                                        |                                               | Problem statement                                                                                                                                                   | 1                                 |

|                                        |                                               | Objectives                                                                                                                                                          | 3                                 |

|                                        | 1.4                                           |                                                                                                                                                                     | 4                                 |

|                                        |                                               | Research methodology                                                                                                                                                | 4                                 |

|                                        | 1.6                                           | Organization of the thesis                                                                                                                                          | 5                                 |

| 2                                      | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | Introduction Wireless communication system and architecture IEEE 802.5.4b/ZigBee Standard Overview Mixer Design parameters 2.4.1 Conversion Gain 2.4.2 Noise Figure | 7<br>7<br>7<br>9<br>10<br>11      |

|                                        |                                               | 2.4.3 Linearity                                                                                                                                                     | 13                                |

|                                        | 2.5                                           | IEEE 802.15.4 Requirement for Noise Figure and IIP3                                                                                                                 | 17                                |

|                                        | 2.6                                           | Low-voltage and low-power RF circuit design techniques                                                                                                              | 18                                |

|                                        |                                               | 2.6.1 Forward-body-bias technique                                                                                                                                   | 18                                |

|                                        |                                               | 2.6.2 Current-reused Technique                                                                                                                                      | 19                                |

|                                        |                                               | 2.6.3 Subthreshold biasing technique                                                                                                                                | 19                                |

|                                        | 2.7                                           | 1 23                                                                                                                                                                | 21                                |

|                                        |                                               | 2.7.1 The Gilbert Cell Mixer                                                                                                                                        | 21                                |

|                                        |                                               | 2.7.2 Folded Mixer                                                                                                                                                  | 22                                |

|                                        |                                               | 2.7.3 Current bleeding mixer                                                                                                                                        | 23                                |

|                                        |                                               | 2.7.4 Bulk driven mixer                                                                                                                                             | 24                                |

|                                        |                                               | / / A Nun-narmonic mixer                                                                                                                                            | 14                                |

|   |                | 2.7.6 Summary of reported mixer                                                        | 26              |

|---|----------------|----------------------------------------------------------------------------------------|-----------------|

|   | 2.8            | Low Noise Amplifier (LNA)                                                              | 27              |

|   | 2.9            | Integrated LNA-Mixer topology                                                          | 27              |

|   | 2.10           | Conclusion                                                                             | 28              |

| 3 | <b>ULT</b> 3.1 | TRA-LOW VOLTAGE AND LOW POWER MIXER Introduction                                       | 28<br>29        |

|   | 3.2            | Design considerations                                                                  | 29              |

|   | 3.3            | Proposed ultra-low voltage design topology                                             | 30              |

|   |                | 3.3.1 Design using $g_m I_D$ methodology                                               | 34              |

|   |                | 3.3.3 PMOS-based LO switching stage with low DC biasing voltage                        | 39              |

|   |                | 3.3.4 Supply voltage headroom and constraint                                           | 40              |

|   |                | 3.3.5 High LO-RF isolation                                                             | 41              |

|   |                | 3.3.6 NMOS-based bleeding transistor reduces RF leakage to power ra                    | ail 45          |

|   |                | 3.3.7 Reduction of parasitic capacitance at the RF-LO mixing node                      | 46              |

|   | 3.4            | Results and Discussions                                                                | 49              |

|   | 3.5            | Conclusion                                                                             | 61              |

| 4 | AT             | RWARD BODY-BIAS CMOS MIXER COUPLED WITH INDUCTION THE BLEEDING TRANSISTOR Introduction | 62<br>62        |

|   |                | Design Considerations                                                                  | 62              |

|   |                | Forward body-bias mixer coupled with bleeding gate inductor                            | 63              |

|   |                | 4.3.1 Integration of inductor at the gate of bleeding transistor                       | 64              |

|   |                | 4.3.2 Stability of The Mixer                                                           | 65              |

|   |                | 4.3.3 Spurious signal at the output port                                               | 67              |

|   |                | 4.3.4 Linearity, IIP3 analysis                                                         | 68              |

|   |                | 4.3.5 Reduced RF current leakage through $C_{gs}$ of bleeding transistor               | 68              |

|   | 4.4            | Temperature Compensation Circuitry                                                     | 69              |

|   | 4.5            | Results and discussions                                                                | 70              |

|   |                | 4.5.1 Forward body-bias mixer coupled with bleeding gate inductor                      | 70              |

|   |                | 4.5.2 Mixer with integration of temperature compensation Circuitry                     | 76              |

|   | 4.6            | Performance comparison with other reported mixer                                       | 80              |

|   | 4.7            | Conclusion                                                                             | 81              |

| 5 | MI             | TRA-LOW VOLTAGE AND LOW POWER INTEGRATED XER Introduction                              | LNA<br>82<br>82 |

|       | 5.2 Design Considerations                                        | 82       |

|-------|------------------------------------------------------------------|----------|

|       | 5.3 Proposed Ultra-Low Voltage Differential Integrated LNA-Mixer | 83       |

|       | 5.4 Results and Discussions                                      | 89       |

|       | 5.5 Conclusion                                                   | 97       |

| 6     | CONCLUSION AND FUTURE WORK 6.1 Overview                          | 98<br>98 |

|       | 6.2 Technical Contributions and Impact of The Thesis             | 98       |

|       | 6.3 Scope of Future Works                                        | 99       |

| REF   | ERENCES                                                          | 101      |

| BIO   | DATA OF STUDENTS                                                 | 107      |

| T TCT | OF DUDI ICATIONS                                                 | 100      |

# LIST OF TABLES

| Table                                                                          |    |

|--------------------------------------------------------------------------------|----|

| 2.1: Summary of other reported mixers                                          | 26 |

| 2.2: Comparison with other integrated LNA-mixers                               | 28 |

| 3.1: Design parameters for the mixer                                           | 38 |

| 3.2: Comparison results between schematic, post layout and measurement results | 57 |

| 3.3: The effect of performance due to PVT variations                           | 59 |

| 3.4: Comparison with other mixers                                              | 60 |

| 4.1: Design parameters for the mixer                                           | 75 |

| 4.2: Performance comparison with other reported mixer                          | 80 |

| 5.1: The effect of performance due to PVT variations                           | 94 |

| 5.2: Design parameters for the mixer                                           | 95 |

| 5.3: Summary results and performance comparison of other LNA- mixer.           | 96 |

# LIST OF FIGURES

| Figur | re                                                                       | Page   |

|-------|--------------------------------------------------------------------------|--------|

| 1.1:  | Supply voltage of reported active mixers (Shirazi et al., 2013)          | 2      |

| 1.2:  | Power consumption of reported mixers (Shirazi et al., 2013)              | 2<br>5 |

| 1.3:  | Research methodology flow                                                | 5      |

| 2.1:  | RF receiver                                                              | 7      |

| 2.2:  | Super-heterodyne receiver                                                | 8      |

| 2.3:  | Direct conversion receiver (DCR)                                         | 9      |

| 2.4:  | Wireless applications in term of coverage and data rate (Le, 2011)       | 10     |

| 2.5:  | Cascaded Noise Figure                                                    | 12     |

| 2.6:  | 1dB compression point                                                    | 13     |

| 2.7:  | Intermodulation in a non-linearity system                                | 14     |

| 2.8:  | Input-output characteristic of a nonlinear system                        | 14     |

| 2.9:  | Corruption of a signal due to intermodulation between two interferers    | 15     |

|       | Third-order intercept point (IIP3)                                       | 15     |

|       | Potential LO self-mixing paths                                           | 16     |

| 2.12: | Cross sectional of the NMOS device with deep N-well structure.           | 18     |

| 2.13: | Current reuse technique                                                  | 19     |

| 2.14: | Gilbert cell                                                             | 21     |

| 2.15: | Folded cascode mixer                                                     | 22     |

| 2.16: | Current bleeding mixer                                                   | 23     |

| 2.17: | Bulk driven mixer                                                        | 24     |

| 2.18: | 2X Subharmonic mixer                                                     | 25     |

| 3.1:  | CMOS current bleeding mixer adapted from (Park el at., 2007)             | 31     |

| 3.2:  | Simplified block diagram for the proposed mixer                          | 32     |

| 3.3:  | Proposed ultra-low voltage CMOS current mixer                            | 33     |

| 3.4:  | Ratio of LO switch current to total DC current                           | 37     |

| 3.5:  | $g_{m}/I_d$ versus overdrive voltage for NMOS                            | 35     |

| 3.6:  | $I_d$ /W versus $g_m$ / $I_d$ voltage for NMOS                           | 35     |

| 3.7:  | g <sub>m</sub> /I <sub>d</sub> versus overdrive voltage for PMOS         | 36     |

| 3.8:  | $I_d$ /W versus $g_m$ / $I_d$ voltage for PMOS                           | 36     |

| 3.9:  | LO leakage for single-ended current bleeding mixer                       | 42     |

|       | Proposed high LO-RF isolation                                            | 43     |

|       | LO-RF leakage path                                                       | 43     |

|       | Small signal model seen into the bleeding transistor                     | 44     |

|       | Small signal RF current leak through RBleed                              | 45     |

|       | Single-ended small signal model for the proposed mixer                   | 46     |

|       | Parasitic capacitor at the source of the switching node                  | 47     |

|       | Simplified small signal model looking into the source of switching stage | 48     |

|       | DC current (schematic/post layout)                                       | 49     |

|       | Probe station                                                            | 50     |

|       | GSGSG probe                                                              | 51     |

|       | Conversion gain versus LO power                                          | 52     |

|       | Conversion gain versus RF frequency                                      | 53     |

|       | Linearity, IIP3                                                          | 54     |

| 3 23. | Output spectrum                                                          | 5/1    |

| 3.24: | LO-RF isolation                                                                       | 55 |

|-------|---------------------------------------------------------------------------------------|----|

| 3.25: | RF-LO isolation                                                                       | 55 |

| 3.26: | LO-IF isolation                                                                       | 56 |

| 3.27: | Noise Figure                                                                          | 56 |

|       | Flicker noise frequency                                                               | 57 |

| 3.29: | Linearity, IIP3 at 0.45V                                                              | 58 |

| 3.30: | Chip Photograph                                                                       | 58 |

|       | Forward body-bias CMOS mixer with inductor at the bleeding transistor                 | 63 |

| 4.2:  | Small signal model with the integration of inductor at the gate                       | 64 |

| 4.3:  | Admittance looking into the NMOS bleeding transistor                                  | 66 |

| 4.4:  | Output Spurious                                                                       | 67 |

| 4.5:  | Proposed mixer with temperature compensation circuitry                                | 69 |

| 4.6:  | V <sub>th</sub> and I <sub>bs</sub> versus V <sub>bs</sub> voltage variation for NMOS | 70 |

| 4.7:  | V <sub>th</sub> and I <sub>bs</sub> versus V <sub>bs</sub> voltage variation for PMOS | 71 |

| 4.8:  | Conversion gain versus LO power                                                       | 71 |

| 4.9:  | Conversion gain versus RF frequency                                                   | 72 |

| 4.10: | IIP3 with 1 MHz of frequency spacing                                                  | 73 |

| 4.11: | Output spectrum                                                                       | 73 |

| 4.12: | LO-RF isolation                                                                       | 74 |

| 4.13: | Noise Figure                                                                          | 74 |

| 4.14: | IIP3 at supply voltage of 0.33V                                                       | 75 |

| 4.15: | Chip micrograph                                                                       | 76 |

| 4.16: | Conversion gain versus temperature                                                    | 77 |

| 4.17: | IIP3 versus temperature                                                               | 77 |

| 4.18: | Noise Figure versus temperature                                                       | 78 |

| 4.19: | Conversion gain versus supply voltage                                                 | 79 |

| 4.20: | DC Power versus supply voltage                                                        | 79 |

|       | Noise Figure versus IF frequency                                                      | 80 |

| 5.1:  | Integrated differential LNA-mixer                                                     | 83 |

| 5.2:  | Low power single-ended LNA-mixer design from (Le, 2011)                               | 84 |

| 5.3:  | Small signal equivalent circuit of integrated LNA-mixer                               | 86 |

| 5.4:  | RF leakage current through parasitic capacitance                                      | 88 |

| 5.5:  | Conversion gain versus ratio current of bleeding/mixer                                | 89 |

| 5.6:  | S11 input reflection                                                                  | 90 |

| 5.7:  | Conversion gain against LO power                                                      | 91 |

| 5.8:  | Conversion gain versus RF frequency                                                   | 91 |

| 5.9:  | 1dB compression point                                                                 | 92 |

|       | IIP3 of integrated LNA-mixer                                                          | 92 |

|       | Noise Figure                                                                          | 93 |

| 5.12: | Layout of integrated LNA-mixer                                                        | 93 |

### LIST OF ABBREVIATIONS

ADC Analog to Digital converter

CG Conversion gain

CMOS Complementary Metal Oxide Semiconductor

DBM Double-balanced mixer

DCR Direct conversion receiver

FOM Figure of Merit

Gm Transconductance

IC Integrated Circuit

IF Intermediate frequency

IIP3 Third-Order Intercept Point

IM Intermodulation

ISM Industrial, Scientific, Medical

LNA Low Noise Amplifier LO Local Oscillator

LPE Layout Parasitic Extraction

LR-WPAN Wireless personal area network

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NF Noise Figure

NMOS N-Channel MOSFET

PA Power Amplifier

PMOS P-Channel MOSFET

PVT Process voltage Temperature

RF Radio Frequency

SNR Signal to noise ratio

SoC System on Chip

VCO Voltage Controlled Oscillator

V<sub>TH</sub> Threshold voltage

WLAN Wireless local area networks WSN Wireless Sensor Network

# **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Motivation

The desire for portability of electronic devices generated global needs for ultra-low power circuits. Ultra-low-voltage and low-power design is the main motivation for this research as increasing number of the electronics devices nowadays are wireless portable devices which are operated by the battery. Low power dissipation is very important for portable devices in order to have maximum battery life-time (Wu et al., 2007). Due to this crucial low power requirement, ultra-low voltage and low-power CMOS radio frequency integrated circuit (RFICs) has been the heat of discussion in recent years to prolong and reduce the weight of the battery (Heiberg et al., 2011).

A low-power implementation of a wireless front-end receiver had been widely reported for application such as Wireless Sensor Network (WSN) (Song et al., 2007 and Shokrani et al., 2014). WSN applications which require very low power and low data rate often adopt ZigBee standard based on the regulation of IEEE 802.15.4. This standard operates in the frequency of 2.4GHz for the short range wireless communication in WSN and very suitable for low power circuit (Manjula & Selvathi, 2012).

The basic building blocks for the RF front-end of a wireless transceiver includes low noise amplifier (LNA), mixer, filters, voltage controlled oscillator (VCO) and power amplifier (PA). One of the main challenges for low-power design for RF front-end is to achieve the desired dynamic performance while minimizing the DC power dissipation. However, minimization of the power dissipation might degrade the dynamic performance of the RF circuitry such as conversion gain and linearity. For example, reducing the DC biasing current of the mixer's transconductance stage will degrade the conversion gain and linearity of the mixer.

### 1.2 Problem statement

Over the years, a lot of researches have been done to meet the demand for wireless communication standard like wireless local area networks (WLAN) which require stringent specifications for high data-rate application. The IEEE 802.15.4 standard was specially developed targeted for Wireless Sensor Network (WSN) applications such as industrial automation, remote monitoring and control applications which require very low power consumption and low complexity. ZigBee standard does not impose severe restrictions on specification such as noise and sensitivity, the design restriction is more on power consumption (Cornetta, 2009). The power consumption required in WSN front-end is expected to be lower compare to other applications due to the relaxed specifications required to support a low data throughput. The focus of Wireless Sensor Network (WSN) protocols is usually on long-range and real-time applications. Low power applications that employ WSN include lighting controls, air conditioning controls, remote meter reading, security, sensors for fire safety residential and industrial automation, automotive control and monitoring, entertainment and health care. A wireless solution to the applications listed is not practical if the high power consumption in wireless devices requires frequent battery replacement or recharge. Since these applications need only low-complexity wireless connectivity with low datarate and low-power wireless solution is feasible.

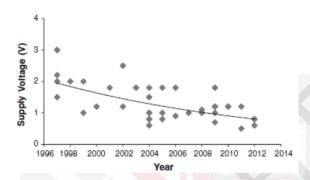

Due to the continuous CMOS technology down scaling to nano-meter level, the proportional downscaling of supply voltage is compulsory to maintain the reliability of the transistor gate-oxide (Hsieh, Lu, 2007). Scaling of CMOS technologies has a great impact on RF circuit design due to the reduction of the supply voltage (Wan, et al., 2012). The supply voltage can be reduced to around 0.5V for application with solar cells (Kousai, 2014). Figure 1.1 illustrates the trend in the supply voltage of the state-of-the-art active mixers that are published from year 1997 to 2012.

Figure 1.1: Supply voltage of reported active mixers (Shirazi et al., 2013)

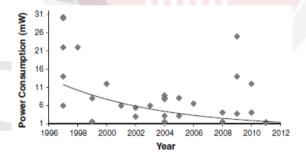

As can be observed from Figure 1.1, the trend line shows that the supply voltage reduces by almost 85 mV per year and the exponential trend line tends to saturate at around 0.8V (Shirazi et al., 2013). Figure 1.2 illustrates the power consumption of the active mixer and it is obviously shows that the power consumption reduces by approximately 0.8mW per year. However, the decrease in the power consumption eventually flattens at around 1 mW which providing a bottleneck in operating the mixer in micro power range.

Figure 1.2: Power consumption of reported mixers (Shirazi et al., 2013)

For digital circuits, small feature size of MOSFET is preferred which is proportional to the down scaling of supply voltage. Most of the electronic system nowadays is based on System on Chip (SoC) which integrates digital, analog and RF signal on a single chip (Hong et al., 2008, and Schweiger et al., 2011). The digital circuits which are integrated with the RF circuits on the same die will require the RF circuits to operate with the same supply voltage in order to simplify the system architecture while ensuring the lowest DC power consumption (Heiberg et al., 2011). Hence, the RF

circuits must able to operate with single supply voltage in order to be compatible with the supply voltage of the digital circuit which poses a new challenge for RF circuits to operate without sacrificing the circuit's performance (Nebojsa, 2008). However, low voltage circuit design usually demands higher biasing current to avoid the dynamic range degradation which results in an increase of power consumption. Low voltage circuit design must come with low current consumption in order to reduce the overall power consumption of the circuit. Hence, low-voltage architecture coupled with low current consumption becomes very challenging to design and is an essential need for portable wireless devices. Various low-voltage and low-power design techniques have been explored and studied to enable the RF circuitry to operate at ultra-low supply voltage while maintaining the dynamic performance of the circuit. Low power consumption is one of the main specification required by ZigBee standard and can be reduced by either lowering down the supply voltage or decreasing the DC current used in the circuit.

Direct conversion receiver (DCR) is the preferred choice of low power and low cost adaptation for the receiver front-end as it directly converts the RF signal to IF signal without using the intermediate stage and external components (Chiou, Lin & Row, 2012). This reduces the overall power consumption of the front-end receiver. One of the major issues associated with DCR is the LO to RF port isolation (Razavi, 1997). The self-mixing produces a DC offset which will degrade the performance of the receiver. Therefore, high isolation between the LO-RF ports is crucial in the effort of alleviating self-mixing (Hsu & Lee, 2006 and Yoon et al., 2011). Typically, cascoded circuit is used to enhance the isolation between the ports (Ahn et al., 2009). However, cascoded structure requires higher voltage headroom to operate and it is not suitable to be implemented for low-voltage circuits. Therefore, low-voltage mixer with high LO-RF isolation is critical for DCR architecture.

The whole system linearity of the receiver front-end is often limited by the linearity of the mixer. The input power of the mixer is relatively large compare to the input power of Low Noise Amplifier (LNA). The linearity of the mixer plays the key role to determine dynamic range of the communication system. The linearity is inversely proportional to the supply voltage and as a result to design a mixer with good linearity become very challenging nowadays as the supply voltage is scaled down to below 1V (Razavi,2007). New circuit design techniques are needed to ensure the circuit to function well while maintaining the linearity performance.

The conventional architecture of receiver front-end consists of discrete components such as low noise amplifier (LNA), mixer, voltage control oscillator (VCO), low pass filter and inter-stage matching network. The extra impedance matching circuitry leads to signal power wastage, supply power overhead and impending parasitic component due to the complexity of the circuitry. Integrated LNA-Mixer is investigated in this thesis that focus on low power implementation. As a conclusion, the ultra-low voltage and low-power techniques used in this design does not degrade the performance of the circuits and meets the requirement for ZigBee application.

#### 1.3 Objectives

The proposed research is carried out in the effort of realizing an ultra-low voltage and low power CMOS mixer and integrated LNA-mixer in compliance with IEEE 802.15.4 ZigBee application. The proposed architectures are realized in 0.13µm, 8 metals, and 1

poly standard CMOS process. In this thesis, the primary objectives of the research are given as:

- 1. To investigate circuits design techniques for ultra-low voltage and low power RF front-end receiver with improved dynamic performance.

- 2. To design and analyze ultra-low voltage and low power new current bleeding CMOS mixer topology at 0.5V of supply voltage.

- 3. To enhance CMOS mixer design in term of power consumption and supply voltage headroom using inductor coupled gate bleeding transistor and forward-body bias techniques at 0.35V of supply voltage.

- 4. To implement and validate mixer as an integrated LNA-mixer in 0.13um technology at 0.5V of supply voltage.

### 1.4 Scope of Work

This thesis will focus on implementation of ultra-low voltage and low-power double balanced mixer and integrated LNA-mixer using 0.13um CMOS technology at the supply voltage of 0.5V and 0.35V. Due to the relaxed requirements of the ZigBee standard with a data rate of 250Kbps, ultra-low power consumption is the most important parameter to consider while maintaining the dynamic performance of the circuit. The dynamic performance of the mixer includes the conversion gain (CG), linearity, IIP3, Noise Figure (NF) and ports to ports isolation. These results will be compared with other reported mixers using the Figure of Merit (FOM) to prove that the proposed mixer has compatible performance while working at low supply voltage and low-power consumption.

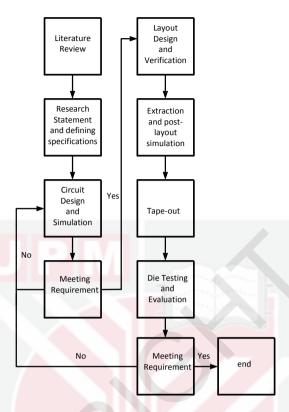

#### 1.5 Research methodology

Figure 1.3 illustrates the research methodology flow for the research. The circuits are designed according to the specifications and simulated using Cadence software to validate its performance. The circuits are fabricated in CMOS 0.13um technology and measurement is performed on the die using probe station to verify its performance. The proposed research is conducted with the aim of designing a ultra-low-voltage and low-power CMOS differential mixer and integrated LNA-mixer. Various low voltage and low power design technique have been studied and explored to enable the mixer to work at supply voltage of 0.5V and 0.35V.

The new CMOS current bleeding mixer is introduced by adapting a combination of NMOS-based current bleeding transistor, PMOS-based LO switching stage and integrated inductors to enable the circuit to operate with ultra-low voltage supply of 0.5V. The DC voltage required for PMOS-based LO switching stage is moving towards ground potential which is independent of positive of power supply and this makes the circuit very attractive for low voltage application. This low-voltage architecture is further utilized to enhance the isolation between the LO and RF ports while maintaining the operation with only 0.5V of supply voltage.

Figure 1.3: Research methodology flow

Another design approach investigated for ultra-low-power and low-voltage CMOS mixer is based on current bleeding mixer topology adapting forward body-bias technique together with the integration of inductors at the gate of bleeding transistors. This approach increases the conversion gain without increasing the DC power consumption of the circuits. Low voltage design couples with low DC current prove to be the breakthrough for micro power RF circuit design. The ultra-low voltage and low power integrated LNA-mixer that allows the sharing of DC current between LAN and mixer is also proposed which can reduce the power consumption.

#### 1.6 Organization of the thesis

This thesis is divided into six chapters. After introducing the research objectives and challenges in chapter 1, chapter 2 starts with a review of the basic wireless receiver architectures, ZigBee standard and the fundamental operation of the mixer. This chapter also covers various topologies for low-voltage and low-power CMOS mixer and integrated LNA-mixer. All topologies are compared their performance in term of conversion gain (CG), third-order intercept point (IIP3), noise figure (NF) and port and port isolation. Chapter 3 provides an overview of the ultra-low voltage and low power mixer design at 0.5V of supply voltage in 0.13µm CMOS technology. In this chapter, a fundamental theory to implement a low-voltage mixer is discussed in depth and novel circuit design technique is introduced to improve LO-RF isolation while still able to operate at low supply voltage. The low-voltage design technique used in this circuit is further utilized to improve the IIP3 of the mixer. Ultra-low voltage mixer without

sacrificing the performance of the mixer is the key contribution from this chapter. Chapter 4 describes a further improvement in the low-voltage and low-power circuit design techniques developed in chapter 3. In this approach, forward body bias is applied to the circuit to reduce the threshold voltage of the transistor in order to reduce the overall voltage headroom of the circuit. Integrated inductor is inserted at the gate of the current bleeding transistor to increase the conversion gain of the mixer without increasing the DC biasing current of the transconductance stage. Mathematical analysis has proven that conversion gain has increased and the circuit is in stable condition as the inductor is integrated at the gate of the bleeding transistor. This mixer is able to work at ultra-low supply voltage of 0.35V. In this chapter as well, ultra-low voltage CMOS mixer with the adaptation of novel temperature compensation circuitry is discussed. The simulations results of mixer are shown and compared with the measurement results. All the experimental result of the fabricated 0.13µm CMOS mixers have been compared with the state of the arts mixer which have been published by other researchers.

Chapter 5 presents an integrated ultra-low voltage and low-power differential integrated LNA-mixer architecture. Due to the low cost requirements by the ZigBee standard, the integrated LNA-mixer will eliminate the needs of external filter and impedance matching circuitry. The DC current from mixer is reused at LNA stage to increase its transconductance for conversion gain enhancement. Furthermore, the mixer stage is folded into the LNA to reduce the voltage headroom required to operate. This integrated LNA-mixer is able to operate at the supply voltage 0.5V. In comparison respective to other reported work, the proposed architecture exhibits the lowest supply voltage headroom consumption and reports power dissipation below 1mW and this architecture proves to be among the lowest in power consumption. Finally, chapter 6 concludes the thesis with technical contributions from the work and on potential future work.

#### REFERENCES

- Ahn, D., Kim, D., & Hong, S. (2009). A K-Band High-Gain Down-Conversion Mixer in 0.18 um CMOS Technology. *IEEE Microwave and Wireless Components letters*, 19(4), 227–229.

- Asgaran, S., & Deen, M. J. (2007). Flicker noise cancellation technique for low-voltage direct-conversion mixers. *Electronics Letters*, 43(19), 7–8.

- Boon, C. C. (2008). *RF IC Design Course Notes*, Nanyang Technological University. Chang, C., Member, S., & Onabajo, M. (2013). IIP3 Enhancement of Subthreshold Active Mixers. *IEEE Transactions on Circuits and Systems II:* Regular Papers, 60(11), 731–735.

- Chen, C., Chiang, P., Jou, C. F., & GHz, A. A. (2009). A Low Voltage Mixer with Improved Noise Figure. *IEEE Microwave and Wireless Components letters*, 19(2), 92–94.

- Chen, J.-D., Lin, Z.-M., & Row, J.-S. (2009). A 5.25-GHz low-power Down Conversion Mixer in 0.18-µm CMOS Technology. *Analog Integrated Circuits and Signal Processing*, 62(3), 301–312.

- Chiou, H.-K, Lin, K.-C, Chen, W.-H, & Juang, Y.-Z (2012). A 1-V 5-GHz Self-Bias Folded-Switch Mixer in 90-nm CMOS for WLAN Receiver, 59(6), 1215–1227.

- Choi, J.-Y. & Lee S.-G. (2004). A 2.45 GHz CMOS Up-conversion Mixer Design Utilizing the Current-reuse Bleeding Technique. *International Journal Electronics*, 91(9), 537–550.

- Chye, C., Anh, M., Seng, K., & Aaron, V. (2010). A Weak-Inversion Low-Power Active Mixer. *IEEE Microwave and Wireless Components letters*, 19(11), 4–7

- Cook, B. W. (2007). Low energy RF transceiver design. University of California at Berkeley.

- Cornetta, G., Touhafi, A., Santos, D. J., & Manuel, V. (2009). A Direct Down-conversion Receiver for Low-power Wireless Sensor Networks, 220–229.

- Dan, S., & Xiaolin, Z. (2010). Low-voltage CMOS Folded-cascode Mixer. *Chinese Journal of Aeronautics*, 23(2), 198–203.

- Darabi, H., & Abidi, A. A. (2000). Noise in RF-CMOS Mixers: A Simple. *IEEE Journal of Solid-state Circuits*, 35(1), 15–25.

- Do, A. V, Boon, C. C., Do, M. A., Member, S., & System, A. O. (2008). A Subthreshold Low-Noise Amplifier Optimized for Ultra-Low-Power Applications in the ISM Band. *IEEE Transactions on Microwave Theory and Techniques*, 56(2), 286–292.

- Douss, S., Touati, F., & Loulou, M. (2008). An RF-LO Current-bleeding Doubly Balanced Mixer for IEEE 802.15.3a UWB MB-OFDM Standard Receivers. *International Journal of Electronics and Communications*, 62(7), 490–495.

- Elyasi, H., Jannesari, A., & Nabavi, A. (2012). A merged LNA and mixer with improved noise figure and gain for software defined radio applications. *IEICE Electronics Express*, 9(3), 165–171.

- Hafez, A. A., Dessouky, M. A., & Ragai, H. F. (2009). Design of a low-power ZigBee receiver front-end for wireless sensors. *Microelectronics Journal*, 40(11), 1561–1568.

- He, S., Saavedra, C. E., & Member, S. (2012). An Ultra-Low-Voltage and Low-Power. *IEEE Transactions on Microwave Theory and Techniques*, 60(2), 311–317.

- Heiberg, A. C., Brown, T. W., Member, S., & Fiez, T. S. (2011). A 250 mV, 352 W GPS Receiver RF Front-end. *IEEE Journal of Solid-State Circuits*, 46(4), 938–949.

- Henrik S, Ali K-S, Asad AA. (2003). A merged CMOS LNA and mixer for a WCDMA receiver. *IEEE Journal of Solid-State Circuit*, 38(6), 1045 50.

- Hong, E.-P., Hwang, Y.-S., & Yoo, H.-J. (2008). Direct Conversion RF Front-end with a Low-power Consumption Technique for 2.4 GHz ISM Band. *IET Microwaves, Antennas & Propagation*, 2(8), 898–903.

- Hsieh, H.-H, & Lu, L.-H (2007). Design of Ultra-Low-Voltage RF Frontends with Complementary Current-Reused Architectures. *IEEE Transactions on Microwave Theory and Techniques*, 55(7), 1445–1458.

- Hsu, H.-M., & Lee, T.-H. (2006). High LO-RF Isolation of Zero-IF Mixer in 0.18 µm CMOS. *Journal of Analog Integrated Circuits and Signal Processing*, 49, 19–25

- Hwang Y-S, Wang S-F, Chen J-J. (2010). A differential multi-band CMOS low noise amplifier with noise cancellation and interference rejection. *International Journal of Electronic and Communications*, 64(10), 897 903.

- Hwang Y-S, Yoo H-J. (2007). A low power folded RF front-end with merged LNA and mixer for ZigBee/Bluetooth. *Proceedings of IEEE Radio and Wireless Symposium*, 85 86.

- Jackson, B. R., & Saavedra, C. E. (2006). A CMOS Subharmonic Mixer with Input and Output Active Baluns, 48(12), 2472–2478.

- Jackson, B. R., Member, S., Saavedra, C. E., & Member, S. (2008). A CMOS Ku-Band 4x Subharmonic Mixer. *IEEE Journal of Solid-State Circuits*, 43(6), 1351–1359.

- Jeong, J., Kim, J., Ha, D. S., & Lee, H.-S. (2011). A reliable ultra-low power merged LNA and mixer design for medical implant communication services. *IEEE NIH Life Science Systems and Applications Workshop*, 402–405.

- Kang, H. S., Lee, S. G., Park, C. S., & Member, S. (2007). A Low LO Power Mixer Utilizing the Body Effect. *IEEE Microwave and Wireless Components letters*, 17(11), 799–801.

- Karanicolas, A. N. (1996). A 2.7-V 900-MHz. *IEEE Journal of Solid-state Circuits*, 31(12), 1939–1944.

- Kaukovuori, J., Järvinen, J. a. M., Jussila, J., & Ryynänen, J. (2008). Efficient current reuse for low-power transceivers. *Analog Integrated Circuits and Signal Processing*, 56(3), 241–244. Kim, J., & Shin, H. (2013). A current-reuse MICS band CMOS RF transmitter for implantable cardioverter telemetry system. *IEICE Electronics Express*, 10(12), 1-4.

- Kim, M., An, H., Kang, Y., Lee, J., & Yun, T. (2012). A Low-Voltage, Low-Power, and Low-Noise UWB Mixer Using Bulk-Injection and Switched Biasing Techniques. *IEEE Transactions on Microwave Theory and Techniques*, 60(8), 2486–2493.

- Kim, S., Choi, J., Lee, J., Koo, B., & Kim, C. (2011). A Subthreshold CMOS RF Front-End Design for Low-Power Band-III T-DMB / DAB Receivers. *ETRI Journal*, 33(6), 969–972.

- Koo, Y.-S. (2013). A design of low-area low drop-out regulator using body bias technique. *IEICE Electronics Express*, 10(19), 1–12.

- Kousai, S. (2014). Recent progress in CMOS RF circuit design. *IEICE Electronics Express*, 11(2), 1–15.

- Kraimia, H., Taris, T., Begueret, J., & Deval, Y. (2011). A 2.4GHz ultra-low Power current-reuse bleeding mixer with resistive feedback. *IEEE International Conference on Electronics, Circuits and Systems (ICECS)*, 488–491.

- Krcmar, M., & Boeck, G. (2010). A broadband folded Gilbert cell CMOS mixer. Analog Integrated Circuits and Signal Processing, 39–44.

- Kwon, Y., Park, S., Park, T., Cho, K., & Lee, H. (2012). An Ultra-Low-Power CMOS Transceiver Using Various Low-Power Techniques for LR-WPAN Applications. *IEEE Transactions on Circuits and Systems I*, 59(2), 324–336.

- Lai D, Chen Y, Wang X, Chen X. (2010). A CMOS Single-Differential LNA and current bleeding CMOS mixer for GPS Receivers. *Proceedings of ICCT*, 677 - 80

- Larson, L. E. (1997). *RF and Microwave Circuit Design for Wireless Communications* (1st ed.). Norwood, MA, USA: Artech House, Inc.

- Le, V. H., Han, S., Lee, J., & Lee, S. (2009). Current-Reused Ultra Low Power, Low Noise LNA + Mixer. *IEEE Microwave and Wireless Components letters*, 19(11), 755–757.

- Le, V. H.(2011).CMOS Receiver front-end for Wireless Communication:For IEEE802.15.4B and DVB Tuner. PhD Dissertation, KAIST.

- Lee, H., & Mohammadi, S. (2007). A 500µW 2.4GHz CMOS Subthreshold Mixer for Ultra Low Power Applications. *IEEE Radio Frequency Integrated Circuits Symposium*, 325–328.

- Lee, S., Wang, L., Chen, T., & Yu, C. (2012). A Low-Power RF Front-End with Merged LNA, Differential Power Splitter and Quadrature Mixer for IEEE 80.15.4 (ZigBee) Applications. *IEEE International Symposium on Circuits and Systems (ISCAS)*, 15–18.

- Lee, S.-G., & Choi, J.-K. (2000). Current-reuse Bleeding Mixer. *Electronics Letters*, 36(8), 696–697.

- Li, J., & Hasan, S. M. R. (2014). An inductive-degenerated current-bleeding LNA-merged CMOS mixer for 866 MHz RFID reader. *Analog Integrated Circuits and Signal Processing*, 80(2), 173-185.

- Liang, K.-H., & Chang, H.-Y. (2011). 0.5–6 GHz low-voltage low-power mixer using a modified cascode topology in 0.18 um CMOS technology. *IET Microwaves, Antennas & Propagation*, 5(2), 167–174.

- Liou, W., Yeh, M., Tsai, C., & Chang, S. (2005). Design and Implementation of a Low-Voltage 2.4-GHz CMOS RF Receiver Front-End for Wireless Communication. *Journal of Marine Science and Technology*, 13(3), 170–175.

- Liu B, Wang C, Ma M, Guo S. (2009). An ultra-low voltage and ultra low power 2.4GHz LNA design. *Radioengineering*, 18(4), 527 31.

- Lu, L.-H. & Chen, H.-S. (2010). Lower the voltage for CMOS RFIC. *Microwave Magazine*, *IEEE*, 11(1), 70-77.

- Mahmou, R., & Faitah, K. (2014). High linearity, low power RF mixer design in 65nm CMOS technology. *International Journal of Electronics and Communications*, 68(9), 883-888.

- Mahmoudi, F., & Salama, C. A. T. (2006). 8 GHz 1V, CMOS quadrature downconverter for wireless applications. *Analog Integrated Circuits and Signal Processing*, 48(3), 185–197.

- Manjula, S., & Selvathi, D. (2012). Design of Low Power 2.4GHz CMOS Cascode LNA with Reduced Noise Figure for WSN Applications. *Wireless Personal Communications*, 70(4), 1965-1976.

- Martins MA, Oliveira LB, Fernandes JR. (2009). Combined LNA and mixer circuits for 2.4 GHz ISM band. *Proceedings of IEEE International Symposium on Circuits and Systems*, 425 428.

- Meng, Z., Zhiqun, L., & Zengqi, W. (2014). Design of ultra low power receiver frontends for 2.4 GHz wireless sensor. *Journal of Semiconductor*, 35(1), 4–11.

- Nebojsa, S., Balankutty, A., Kinget, P. R., & Tsividis, Y. (2008). A 2.4-GHz ISM-Band Sliding-IF Receiver with a 0.5-V Supply. *IEEE Journal of Solid-state Circuits*, 43(5), 1138–1145

- Nguyen T-K, Oh N-J, Le V-H, Lee S-G. (2006). A low-power CMOS direct conversion receiver with 3-dB NF and 30-kHz flicker-noise corner for 915-MHz band IEEE 802.15.4 ZigBee standard. *IEEE Transactions on Microwave Theory Techniques*, 54(2), 735 41.

- Nguyen T-K., Kim C-H., Ihm G-J, Yang M-S, Lee S-G. (2004). CMOS low-noise amplifier design optimization techniques. *IEEE Transactions on Microwave Theory and Techniques*, 52(5), 1433 1442.

- Nguyen, T.-K, Krizhanovskii, V., Lee, J., Han, S.-K, Lee, S.-G, Kim, N., et al. (2006). A Low-Power RF Direct-Conversion. *IEEE Transactions on Microwave Theory and Techniques*, 54(12), 4062–4071.

- Noh NM, Zulkifli TZA. (2006). A 1.4dB Noise Figure CMOS LNA for W-CDMA Application. *Proceedings of RFM*, 143 48.

- Oh, N.-J. and Lee, S.-G. (2006). Building a 2.4-GHz radio transceiver using IEEE 802.15.4. *IEEE Circuits Devices Mag.*, 21, 43-51.

- Park, J., Lee, C., Kim, B., & Laskar, J. (2006). Design and Analysis of Low Flicker-Noise CMOS Mixers for Direct-Conversion Receivers. *IEEE Transactions on Microwave Theory and Techniques*, 54(12), 4372–4380.

- Perumana, B. G.(2007). Low-Power CMOS Front-Ends for Wireless Personal Area Networks. PhD Dissertation, Georgia Institute of Technology.

- Ramiah, H., Kanesan J., & Zulkifli, T. Z. A. (2013). A CMOS Up-conversion Mixer in 0.18μm Technology for IEEE 802.11a WLAN Application, *IETE Journal of Research*, 59(4), 454-460.

- Razavi, B. (1997). Design Considerations for Direct-Conversion. *IEEE Transaction on Circuit and Systems*, 44(6), 428–435.

- Razavi, B. (2006). RF Microelectronics": Prentice Hall PTR, chap.2.

- Razavi, B. (2007). Design Considerations for Future RF Circuits. 2007 IEEE International Symposium on Circuits and Systems, 741–744.

- Saberkari, A., Shokouhi, S. B., & Abrishamifar, A. (2009). A low voltage highly linear CMOS up conversion mixer based on current conveyor. *IEICE Electronics Express*, 6(13), 930–935.

- Schmitz, O., Hampel, S. K., Orlob, C., Tiebout, M., & Rolfes, I. (2010). Body effect up- and down-conversion mixer circuits for low-voltage ultra-wideband operation. *Analog Integrated Circuits and Signal Processing*, 64(3), 233–240.

- Schweiger, K., & Zimmermann, H. (2011). Double-Gilbert mixer with enhanced linearity in 65 nm low-power CMOS technology. *Analog Integrated Circuits and Signal Processing*, 71(2), 313–317.

- Seo, H., Park, Y., Park, W., Kim, D., Lee, M., Kim, H., & Choi, P. (2008). System Design Considerations for a ZigBee RF Receiver with regard to Coexistence with Wireless Devices in the 2.4GHz ISM-band. *KSII Transactions on Internet and Information Systems*, 2(1), 37–50.

- Shaeffer, D. K. (1998). The Design and Implementation of Low-Power CMOS Radio Receivers", Stanford University.

- Shirazi, A. H. M., & Mirabbasi, S. (2013). An ultra-low-voltage ultra-low-power CMOS active mixer. *Analog Integrated Circuits and Signal Processing*, 77(3), 513–528.

- Shokrani, M. R., Khoddam, M., Hamidon, M. N. B., Kamsani, N. A., Rokhani, F. Z., & Shafie, S. Bin. (2014). An RF Energy Harvester System Using UHF Micropower CMOS Rectifier Based on a Diode Connected CMOS Transistor. *The Scientific World Journal*, 2014.

- Song, T., Oh, H., Yoon, E., & Hong, S. (2007). A Low-Power 2.4-GHz Current-Reused Receiver Front-End and Frequency Source for Wireless Sensor Network. *IEEE Journal of Solid-State Circuits*, 42(5), 1012–1022.

- Sullivan, P. J., Xavier, B. A., & Ku, W. H. (1997). Low Voltage Performance of a Microwave CMOS Gilbert Cell Mixer. *IEEE Journal of Solid-state Circuits*, 32(7), 1151–1155.

- Tae Wook, K., Bonkee, K., & Kywro, L. (2003). Highly linear RF CMOS amplifier and mixer adopting MOSFET transconductance linearization by multiple gated transistors. In *Radio Frequency Integrated Circuits RFIC Symposium* 2003 IEEE, 107–110.

- Tang, C., Wu, C., Feng, W., & Liu, S. (2001). A 2.4 GHz Low Voltage CMOS Down Conversion Double-Balanced Mixer. *IEICE Trans. Electron*, (8), 1084–1091.

- Terrovitis, M. T., Member, S., & Meyer, R. G. (1999). Noise in Current-Commutating CMOS Mixers. *IEEE Journal of Solid-State Circuits*, 34(6), 772–783.

- Vidojkovic, V., Tang, J. Van Der, Leeuwenburgh, A., & Roermund, A. H. M. V. (2005). A Low-Voltage Folded-Switching Mixer in 0.18 um CMOS. *IEEE Journal of Solid-state Circuits*, 40(6), 1259–1264.

- Villegas, A., Váquez, D., & Rueda, A. (2010). A Low Power Low Voltage Mixer for 2.4GHz Applications in CMOS-90nm Technology. *IEEE 13th International Symposium on Design and Diagnostics of Electronic Circuits and Systems* (DDECS), 44–47.

- Wan, Q., Wang, C., & Sun, J. (2012). Design of a Low Voltage Highly Linear 2.4 GHz Up-Conversion Mixer in 0.18 µm CMOS Technology. Wireless Personal Communications, 70(1), 57–68.

- Wan, Q., Wang, C., & Yu, F. (2012). Design of a 2.4 GHz High-Performance Up-Conversion Mixer with Current Mirror Topology. *Radioengineering*, 21(2), 752–757.

- Wang, R., Su, Y., Chien, H., Chuang, C., Hsiao, H., Tu, C., & Juang, Y. (2012). A concurrent dual-band folded-cascode mixer using a LC-tank biasing circuit. *Microelectronics Journal*, 43(12), 1010–1015.

- Wang, S and Huang, B.-Z. (2011). A HIGH-GAIN CMOS LNA FOR 2.4/5.2-GHZ WLAN APPLICATIONS. *Progress in Electromagnetics Research*, 21(May), 155–167.

- Wei, B., Dai, Y., Wang, J., Matsuoka, T., & Taniguchi, K. (2010). Design of a low-voltage CMOS mixer based on variable load technique. *IEICE Electronics Express*, 7(7), 473–479.

- Wei, H.-C., Hsiao, C.-L., & Weng, R.-M. (2013). A Broadband High Linearity Current-Reuse Bulk-Controlled Mixer for 4g Applications. *Progress in Electromagnetics Research*, *138*, 337–350.

- Wei, H.-C., Hsiao, C.-L., & Weng, R.-M. (2013). A Broadband Low Power High Isolation Double-Balanced Subharmonic Mixer for 4g Applications. *Progress in Electromagnetics Research*, 138, 143–155.

- Wei, H. et al., (2010). Flicker Noise and Power Performance of CMOS Gilbert Mixers Using Static and Dynamic Current-Injection Techniques. *Proceedings of Asia-Pacific Microwave Conference* 2010, 542–545.

- Wu, D., Huang, R., Wong, W., & Wang, Y. (2007). A 0.4-V Low Noise Amplifier Using Forward Body Bias Technology for 5 GHz Application. *IEEE Microwave and Wireless Components letters*, 17(7), 543–545.

- Wu, J., Chen, C., & Ji, X. (2013). A 1.2 V high conversion gain mixer with reused gm stage in 65 nm CMOS, 10(11), 1–5.

- Xuan, K., Tsang, K. F., Lee, S. C., & Lee, W. C. (2009). High-performance Current Bleeding CMOS Mixer. *Electronics Letters*, 45(19), 979.

- Yoon, D.-Y., Yun, S.-J., Cartwright, J., Han, S.-K., & Lee, S.-G. (2011). A High Gain Low Noise Mixer with Cross-Coupled Bleeding. *IEEE Microwave and Wireless Components Letters*, 21(10), 568–570.

- Yoon, J., Member, S., Kim, H., Park, C., Member, S., Yang, J., Kim, B. (2008). A New RF CMOS Gilbert Mixer with Improved Noise Figure and Linearity. *IEEE Transactions on Microwave Theory and Techniques*, 56(3), 626–631.

- Zeng, Y., Luo, Y., Zhang, J., Gong, Z., & Tan, H.-Z. (2013). A low power CMOS voltage reference based on body effect. *IEICE Electronics Express*, 10(8), 1–6

- Ziabakhsh, S., Nirouei, M., Saberkari, A., & Rad, H. A. (2009). Reduction Parasitic Capacitance in Switching Stage RF-CMOS Gilbert Mixer for 2 .4 GHz Application. *IEEE International Conference on Electronics, Circuits, and Systems*, 2(4), 615–618.

- Zuezhen W, Robert W. (2004). A novel low power low voltage LNA and mixer for WLAN IEEE 802.11A standard. *Proceedings of IEEE Topical Meet. SIRF*, 231 234.