# **UNIVERSITI PUTRA MALAYSIA**

NEUTRAL-POINT-CLAMPED MULTILEVEL INVERTER DEVELOPMENT FOR TOTAL HARMONIC DISTORTION (THD) REDUCTION

SHARIFAH SAKINAH BINTI TUAN OTHMAN

FK 2014 110

### NEUTRAL-POINT-CLAMPED MULTILEVEL INVERTER DEVELOPMENT FOR TOTAL HARMONIC DISTORTION (THD) REDUCTION

By

SHARIFAH SAKINAH BINTI TUAN OTHMAN

MASTER OF SCIENCE

UNIVERSITI PUTRA MALAYSIA

2014

DEDICATION

# TO MY BELOVED PARENTS, MY BROTHERS, MY SISTERS, AND MY

FRIENDS.

Abstract of thesis presented to the Senate of Universiti Putra Malaysia in fulfillment of the requirement for the degree of Master of Science

#### NEUTRAL-POINT-CLAMPED MULTILEVEL INVERTER DEVELOPMENT FOR TOTAL HARMONIC DISTORTION (THD) REDUCTION

By

#### SHARIFAH SAKINAH BINTI TUAN OTHMAN

August 2014

#### Supervisor Faculty : Nashiren Farzilah Binti Mailah, PhD : Engineering

Over the last few decades, the Multilevel Inverter (MI) has attracted the attention of many researchers involved in this area of study. The MI is a new generation of DC-AC inverter that offers many advantages due to its features as compared to the conventional inverter as it is more suitable for handling large motor and high power applications. Mainly, it offers dv/dt stress reduction on switching devices due to its small voltage increment steps. Various methods have been used to determine the switching angle while constructing this circuit. Another favourable feature of this device is that it allows the Multilevel Inverter to operate at high voltages with low Total Harmonics Distortion (THD) without the use of a transformer.

In this work, a three phase five-level Neutral-Point-Clamped Multilevel Inverter (NPCMI) has been investigated with the focus on determining its switching angle by using a proposed new Graphical Method Analysis (GMA) in order to obtain a lower THD output voltage percentage. The triggering angle and duration of the switching devices were determined and tested in order to achieve the finest sinusoidal-like output voltage waveform. The simulation model of a three phase NPCMI was modelled and the triggering sequences were tested to validate the performance of the MI. A simulation model of the three phase NPCMI was designed and developed using the Matlab/Simulink software package to analyse the performance. The THD of the output voltages with a variable switching frequency were measured and compared with the previous three-level NPCMI and other types of MI.

In conclusion, a new technique to predict the improved switching angle of the three phase NPCMI is introduced to obtain a reduced THD output voltage waveform. The simulation has been verified by using a mathematical equation representation and also by comparison with the works of other researchers. From this work, a three phase five-level NPCMI that possesses a lower THD output voltage waveform has been successfully developed.

Abstrak thesis yang dikemukakan kepada Senat Universiti Putra Malaysia sebagai memenuhi keperluan untuk ijazah Master Sains

#### PEMBANGUNAN PENYONSANG BERBILANG ARAS TITIK NEUTRAL TERAPIT UNTUK PENGURANGAN JUMLAH HEROTAN HARMONIK (JHH)

Oleh

#### SHARIFAH SAKINAH BINTI TUAN OTHMAN

**Ogos 2014**

# Pengerusi:Nashiren Farzilah Binti Mailah, PhDFakulti:Kejuruteraan

Sejak beberapa dekad kebelakangan ini, Penyonsang Berbilang Aras (PBA) telah menarik minat ramai penyelidik untuk terlibat dalam bidang ini. Penyonsang Pelbagai Peringkat (PPP) ini adalah generasi baru bagi penyonsang Arus Terus (AT)-Arus Ulang-alik (AU) yang menawarkan banyak kebaikan kerana ciri-cirinya berbanding penyonsang konvensional kerana ia lebih sesuai untuk mengendalikan motor yang besar dan aplikasi kuasa tinggi. Keutamaannya, ia menawarkan pengurangan tekanan pada dv/dt pada peranti suis kerana kenaikan kecil dalam voltan. Pelbagai kaedah telah digunakan untuk menentukan sudut pensuisan semasa membina litar ini. Satu lagi ciri yang baik daripada PBA ialah ia membolehkan PBA ini beroperasi pada voltan tinggi pada Jumlah Herotan Harmonik (JHH) yang rendah tanpa menggunakan pengubah.

Dalam kajian ini, PBA Titik Neutral Terapit Lima Aras 3-fasa telah diselidik dengan fokus untuk menentukan sudut pensuisannya menggunakan Analisis Kaedah Grafik untuk mendapatkan peratusan JHH voltan yang lebih rendah. Sudut pensuisan telah ditentukan dan diuji untuk mencapai seperti gelombang keluaran voltan yang terbaik. Model simulasi PBA Titik Neutral Terapit Lima Aras 3-fasa telah dimodelkan dan sudut pensuisan telah diuji untuk mengesahkan prestasi PBA.

Model simulasi PBA Titik Neutral Terapit Lima Aras 3-fasa telah direka dan dibangunkan menggunakan pakej perisian Matlab/Simulink untuk menganalisis prestasinya. JHH keluaran voltan dengan berbilang sudut pensuisan diukur dan dibandingkan dengan tiga tahap bertingkat Penyonsang Berbilang Aras (PBA) Titik Neutral Terapit Lima Aras 3-fasa sebelumnya dan lain-lain jenis PBA

Sebagai kesimpulan, satu teknik baru untuk meramalkan sudut pensuisan yang ditambah baik diperkenalkan kepada PBA Titik Neutral Terapit Lima Aras 3-fasa untuk mendapatkan JHH keluaran gelombang voltan yang dikurangkan. Simulasi telah disahkan dengan perisian simulasi Matlab/Simulink dan juga dibandingkan dengan hasil

kerja lain-lain penyelidik. Dari kerja-kerja ini, PBA Titik Neutral Terapit Lima Aras 3fasa bertingkat yang mempunyai gelombang keluaran voltan yang rendah Jumlah JHH telah berjaya dibangunkan.

#### ACKNOWLEDGEMENTS

All praise to supreme Almighty Allah swt, the only creator, cherisher, sustainer, and efficient assembler of the world and galaxies whose blessings and kindness have enabled me to accomplish this project successfully.

I also would like to take this opportunity to greatfully acknowledge the guidance, advice, support and encouragement received from my supervisor, Dr Nashiren Farzilah Binti Mailah who keeps advising and commenting throughout this project until it turns to real success.

A great appreciation is expressed to Prof. Dr. Ishak Aris for his valuable remarks, help, advice, and encouragement. Furthermore, I would like to thank my colleagues especially my labmate Mr. Arash Toudeshki for his kind assistance and guidance. Deepest appreciation also goes to the Faculty of Engineering for providing the facilities and the components required for undertaking this project.

Finally, words alone cannot express the thanks I owe to my beloved father, Tuan Othman Bin Tuan Abdullah, my late mother, Che' Aminah Binti Hj. Ismail, my younger brother, Syed Abdul Latiff Bin Tuan Othman and also other siblings for prayers and helps given to me in so many ways.

I certify that a Thesis Examination Committee has met on 18<sup>th</sup> February 2014 to conduct the final examination of Master Science on her thesis entitled "**Neutral-Point-Clamped Multilevel Inverter Development for Total Harmonic Distortion (THD) Reduction**" in accordance with the Universities and University Colleges Act 1971 and the Constitution of the Universiti Putra Malaysia [P.U.(A) 106] 15 March 1998. The Committee recommends that the student be awarded the Master of Science.

Members of the Thesis Examination Committee were as follows:

#### Nasri bin Sulaiman, PhD

Senior Lecturer Faculty of Engineering Universiti Putra Malaysia (Chairman)

#### Noor Izzri bin Abdul Wahab, PhD

Senior Lecturer Faculty of Engineering Universiti Putra Malaysia (Internal Examiner)

#### Mohd Zainal Abidin bin Ab. Kadir, PhD

Professor Faculty of Engineering Universiti Putra Malaysia (Internal Examiner)

#### Ismail Musirin, PhD

Associate Professor Universiti Teknologi MARA Malaysia (External Examiner)

#### NORITAH OMAR, PhD

Associate Professor and Deputy Dean School of Graduate Studies Universiti Putra Malaysia

Date: 19 September 2014

This thesis submitted to the Senate of Universiti Putra Malaysia and has been accepted as fulfilment of the requirement for the degree of Master of Science. The members of the Supervisory Committee were as follows:

### Nashiren Farzilah Mailah, PhD

Senior Lecturer Faculty of Engineering University Putra Malaysia (Chairman)

#### Ishak Aris, PhD, Professor Faculty of Engineering University Putra Malaysia (Member)

**BUJANG KIM HUAT, PhD** Professor and Dean School of Graduate Studies Universiti Putra Malaysia

Date:

#### **Declaration by Graduate Student**

I hereby confirm that:

- this thesis is my original work;

- quotations, illustrations and citations have been duly referenced;

- this thesis has not been submitted previously or concurrently for any other degree at any other intitutions;

- intellectual property from the thesis and copyright are fully-owned by Universiti Putra Malaysia, as according to the Universiti Putra Malaysia (Research) Rules 2012;

- written permission must be obtained from supervisor and the office of Deputy Vice-Chancellor (Research and Innovation) before thesis is published (in form of written, printed or in electronic form) including books, journals, modules, proceedings, popular writings, seminar papers, manuscripts, posters, reports, lecture notes, learning modules or any other materials as stated in the University Putra Malaysia (Research) Rules 2012;

- there is no plagiarism or data falsification/fabrication in the thesis, and scholarly integrity is upheld as according to the Universiti Putra Malaysia (Research) Rules 2012. The thesis has undergone plagiarism detection software.

| Signature:          | Date: |

|---------------------|-------|

| Name and Matric No: |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

|                     |       |

### **Declaration by Members of Supervisory Committee**

This is to confirm that:

- the research conducted and the writing of this thesis was under our supervision;

- supervision responsibilities as stated in the Universiti Putra Malaysia (Graduate Studies) Rules 2003 (Revision) 2012-2013) are adhered to.

Signature:\_\_\_\_\_

Name of Chairman of Supervisory Committee Dr. Nashiren Farzilah Mailah, PhD

Signature:\_\_\_\_\_

Name of Member of Supervisory Committee: Professor Ishak Aris, PhD

### TABLE OF CONTENTS

|     |       |                                                          | Page             |

|-----|-------|----------------------------------------------------------|------------------|

|     | ГRACT |                                                          | i                |

|     | ГRAK  |                                                          | ii               |

|     |       | EDGEMENTS                                                | iv               |

|     | ROVAL |                                                          | V<br>            |

|     | LARAT |                                                          | vii              |

|     | OF TA |                                                          | X                |

|     |       | BREVIATIONS                                              | xi<br>xiv        |

|     | OF SY |                                                          | XIV              |

|     | 01 01 |                                                          |                  |

| СНА | PTER  |                                                          |                  |

| 1   | INT   | RODUCTION                                                |                  |

|     | 1.1   | Background                                               | 1                |

|     | 1.2   | Problem Statement                                        |                  |

|     | 1.3   | Aim and Objectives                                       | 2                |

|     | 1.4   | Scope of Work                                            | 2<br>2<br>3<br>3 |

|     | 1.5   |                                                          |                  |

|     | 1.6   | Thesis Layout                                            | 3                |

| 2   | LIT   | ERATURE REVIEW                                           |                  |

|     | 2.1   | Introduction                                             | 5                |

|     | 2.2   | Introduction to Multilevel Inverter                      | 5                |

|     | 2.3   | Neutral-Point-Clamped Multilevel Inverter                | 6                |

|     | 2.4   | Current Switching Strategies Used in Multilevel Inverter | 9                |

|     | 2.5   | Total Harmonic Distortion                                | 11               |

|     | 2.6   | Comparison Between Others Topologies in General          | 14               |

|     | 2.7   | Applications of Multilevel Inverter                      | 16<br>17         |

|     | 2.8   | Summary                                                  | 17               |

| 3   | ME    | THODOLOGY                                                |                  |

|     |       | Introduction                                             | 18               |

|     | 3.2   | Design of Five-level NPCMI Simulation Model              | 20               |

|     | 3.3   | Method of Switching Angle Calculation                    | 26               |

|     |       | 3.3.1 Equal Step Width Method                            | 26               |

|     |       | 3.3.2 Modified Step Width Method                         | 29               |

|     | 2.4   | 3.3.3 Proposed Graphical Method Analysis (GMA)           | 30               |

|     | 3.4   | Performance of NPCMI under Varying Switching Frequency   | 37               |

|     | 3.5   | Summary                                                  | 38               |

| 4   |       | SULTS AND DISCUSSIONS                                    | -                |

|     | 4.1   | Introduction                                             | 39               |

|     | 4.2   | Scope of Study                                           | 39               |

|       | 4.3   | Results of Methods of Switching Angle Calculation      | 39  |

|-------|-------|--------------------------------------------------------|-----|

|       |       | 4.3.1 Equal Step Width Method Results and Discussion   | 40  |

|       |       | 4.3.2 Modified Step Width Method (MSWM) Results and    | 43  |

|       |       | Discussion                                             |     |

|       |       | 4.3.3 Graphical Method Analysis (GMA) Results and      | 46  |

|       |       | Discussion                                             | 70  |

|       | 4.4   | Three Phase Five-level NPCMI Using Graphical Method    | 50  |

|       |       | Analysis Results and Discussion With Various Loads     |     |

|       | 4.5   | Three Phase Seven-level NPCMI Analysis                 | 79  |

|       | 4.6   | Comparison with previous work                          | 84  |

|       | 4.7   | Performance of NPCMI under Varying Switching Frequency | 86  |

|       | 4.8   | Summary                                                | 94  |

|       |       |                                                        |     |

| 5     | CON   | CLUSIONS AND RECOMMENDATIONS                           |     |

|       | 5.1   | Conclusions                                            | 95  |

|       | 5.2   | Future Works and Recommendations                       | 96  |

|       |       |                                                        |     |

| REFER | ENCE  | S                                                      | 97  |

| APPEN | DICES | S                                                      | 102 |

|       |       | F THE STUDENT                                          | 111 |

| PUBLI |       |                                                        | 112 |

|       |       |                                                        |     |

|       |       |                                                        |     |

C

# LIST OF TABLES

| Table |                                                                                                                   | Page |

|-------|-------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Switching state of single phase five-level NPCMI                                                                  | 9    |

| 2.2   | THD percentage comparison between different switching techniques                                                  | 12   |

| 2.3   | THD percentage comparison between different switching techniques for five-level Multilevel Inverter               | 13   |

| 2.4   | THD percentage comparison between different modulation techniques for seven-level Multilevel Inverter             | 13   |

| 3.1   | Switching state for five-level NPCMI for one phase leg                                                            | 26   |

| 3.2   | Pulse width and phase delay for each phase switches Equal State<br>Space Width Method                             | 29   |

| 3.3   | Pulse width and phase delay for each phase switches Modified State<br>Space Width Method                          | 30   |

| 3.4   | Pulse width and phase delay for three phase five-level NPCMI for<br>each phase switches Graphical Method Analysis | 32   |

| 3.5   | Switching state for seven-level NPCMI based on development for one phase leg                                      | 33   |

| 3.6   | Pulse width and phase delay for three phase five-level NPCMI for<br>each phase switches Graphical Method Analysis | 36   |

| 4.1   | Comparison the V <sub>LL</sub> THD between three different methods                                                | 49   |

| 4.2   | THD value of three phase five-level NPCMI for resistive load                                                      | 63   |

| 4.3   | THD value of three phase five-level NPCMI for resistive inductive load                                            | 78   |

| 4.4   | Comparison THD with three different levels of NPCMI (resistive load, $R=100\Omega$ )                              | 85   |

| 4.5   | Comparison THD values with other works for five-level MI                                                          | 85   |

| 4.6   | Comparison THD values with other works for seven-level MI                                                         | 86   |

| 4.7   | THD (%) for resistive and inductive load                                                                          | 90   |

# LIST OF FIGURES

| Figure |                                                                                                     | Page |

|--------|-----------------------------------------------------------------------------------------------------|------|

| 2.1    | Basic structure of three phase NPCMI                                                                | 8    |

| 2.2    | Modulation methods for NPCI                                                                         | 10   |

| 2.3    | Basic structure of three-level flying capacitor topology                                            | 14   |

| 2.4    | Basic structure of three-level cascaded H-bridge topology                                           | 15   |

| 3.1    | Flowchart of the overall project in developing three phase NPCMI                                    | 19   |

| 3.2    | Block diagram NPCMI system                                                                          | 20   |

| 3.3    | DC power supply circuit diagram for NPCMI                                                           | 20   |

| 3.4    | Three phase five-level NPCMI power circuit                                                          | 21   |

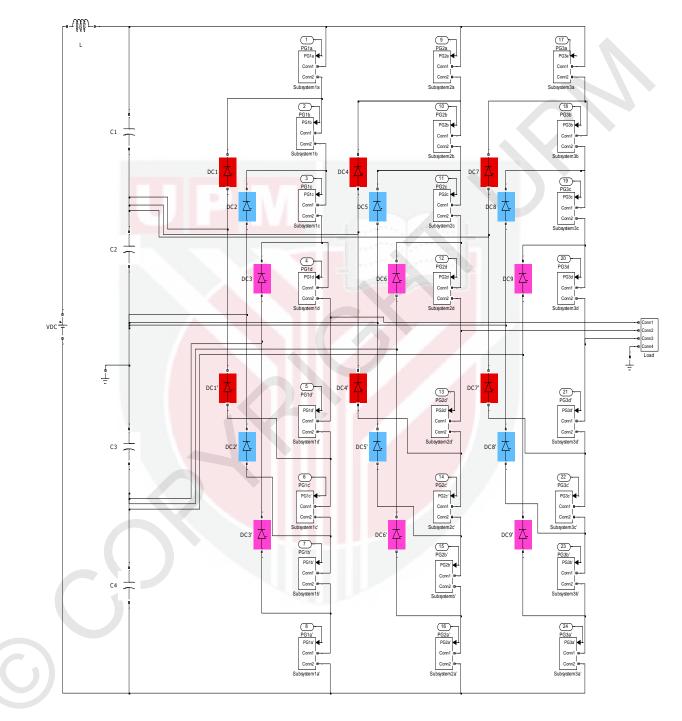

| 3.5    | Subsystem circuit diagram for each switching block                                                  | 23   |

| 3.6    | Loads used in three phase five-level NPCMI model. (a): Resistive load (b): Resistive inductive load | 23   |

| 3.7    | Complete circuit of three phase five-level NPCMI simulation model                                   | 25   |

| 3.8    | Degree of angles to determine pulse width and phase delay for Equal<br>Step Width Method            | 27   |

| 3.9    | Degree of angles to determine pulse width and phase delay for<br>Modified Step Width Method         | 29   |

| 3.10   | Illustrated switching angle using GMA for five-level NPCMI                                          | 31   |

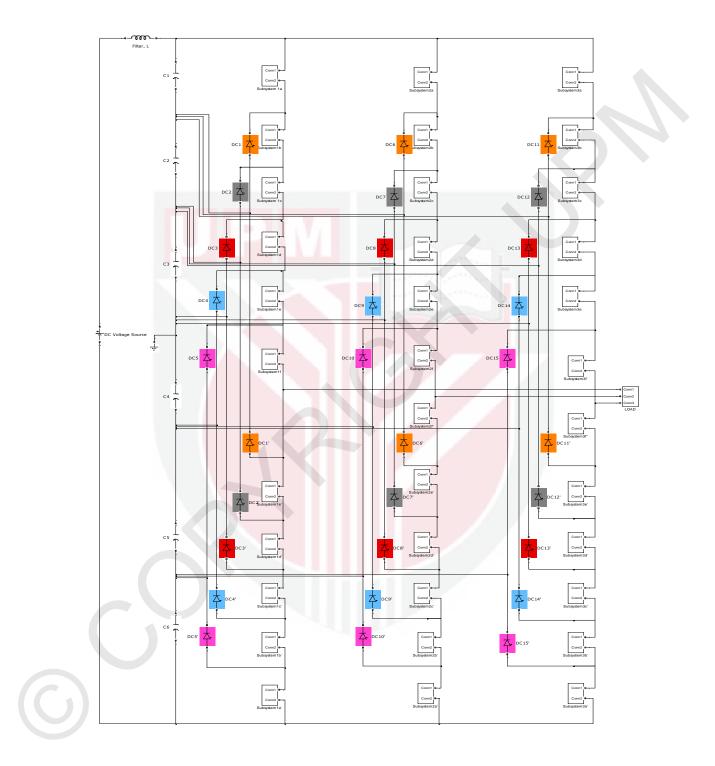

| 3.11   | Matlab/Simulink model for three phase seven-level NPCMI                                             | 34   |

| 3.12   | Illustrated switching angle using graphical method for seven-level NPCMI                            | 37   |

| 4.1    | Switching angle for IGBTs in positive region of phase A                                             | 40   |

| 4.2    | Switching angle for IGBTs in negative region of phase A                                             | 41   |

| 4.3    | Output voltage waveform for-line-to-neutral voltage (V <sub>LN</sub> ) for phase                    | 41   |

| 4.4    | Output voltage waveform for line-to-line voltage (VLL) for phase A                                  | 42   |

| 4.5    | Line-to-line voltage (V <sub>LL</sub> ) waveform for ESWM                                           | 42   |

| 4.6    | Line-to-line voltage (V <sub>LL</sub> ) FFT waveform for ESWM                                       | 43   |

| 4.7    | Switching angle for IGBTs in positive region of phase A                                             | 44   |

| 4.8    | Switching angle for IGBTs in negative region of phase A                                             | 44   |

| 4.9    | Output voltage waveform for line-to-neutral voltage $(V_{LN})$ for phase A                          | 45   |

| 4.10   | Output voltage waveform for line-to-line voltage ( $V_{LL}$ ) for phase A                           | 45   |

| 4.11   | Line-to-line voltage ( $V_{LL}$ ) waveform for MSWM                                                 | 46   |

| 4.12   | Line-to-line voltage $(V_{LL})$ FFT waveform for MSWM                                               | 46   |

| 4.13   | Switching angle for IGBTs in positive region of phase A                                             | 47   |

| 4.14   | Switching angle for IGBTs in negative region of phase A                                             | 47   |

| 4.15   | Output voltage waveform for line-to-neutral voltage $(V_{LN})$ for phase A                          | 48   |

| 4.16   | Output voltage waveform for line-to-line voltage (V <sub>LL</sub> ) for phase A                     | 48   |

| 4.17   | Line-to-line voltage (V <sub>LL</sub> ) waveform for GMA                                            | 49   |

| 4.18   | Line-to-line voltage (VLL) FFT waveform for GMA                                                     | 49   |

| 4.19 | Illustrate of switching angles for Graphical Method Analysis                    | 50  |

|------|---------------------------------------------------------------------------------|-----|

| 4.20 | Line-to-neutral voltage ( $V_{LN}$ ) output waveform for R=50 $\Omega$          | 51  |

| 4.21 | Line-to-line voltage output waveform for $R=50\Omega$                           | 51  |

| 4.22 | Output line current ( $I_L$ ) waveform for R=50 $\Omega$                        | 52  |

| 4.23 | Line-to-neutral voltage ( $V_{LN}$ ) waveform for R=50 $\Omega$                 | 52  |

| 4.24 | Line-to-neutral voltage (V <sub>LN</sub> ) FFT waveform for R=50 $\Omega$       | 53  |

| 4.25 | Line-to-line voltage ( $V_{LL}$ ) waveform for R=50 $\Omega$                    | 53  |

| 4.26 | Line-to-line voltage ( $V_{LL}$ ) FFT waveform for R=50 $\Omega$                | 53  |

| 4.27 | Line current ( $I_L$ ) waveform for R=50 $\Omega$                               | 54  |

| 4.28 | Line current (I <sub>L</sub> ) FFT waveform for R=50 $\Omega$                   | 54  |

| 4.29 | Line-to-neutral voltage ( $V_{LN}$ ) output waveform for R=100 $\Omega$         | 55  |

| 4.30 | Line-to-line voltage output waveform for $R=100\Omega$                          | 55  |

| 4.31 | Output line current ( $I_L$ ) waveform for R=100 $\Omega$                       | 56  |

| 4.32 | Line-to-neutral voltage ( $V_{LN}$ ) waveform for R=100 $\Omega$                | 56  |

| 4.33 | Line-to-neutral voltage ( $V_{LN}$ ) FFT waveform for R=100 $\Omega$            | 57  |

| 4.34 | Line-to-line voltage ( $V_{LL}$ ) waveform for R=100 $\Omega$                   | 57  |

| 4.35 | Line-to-line voltage ( $V_{LL}$ ) FFT waveform for R=100 $\Omega$               | 58  |

| 4.36 | Line current (I <sub>L</sub> ) waveform for $R=100\Omega$                       | 58  |

| 4.37 | Line current (I <sub>L</sub> ) FFT waveform for $R=100\Omega$                   | 59  |

| 4.38 | Line-to-neutral voltage ( $V_{LN}$ ) output waveform for R=150 $\Omega$         | 59  |

| 4.39 | Line-to-line voltage output waveform for $R=150\Omega$                          | 60  |

| 4.40 | Output line current ( $I_L$ ) waveform for R=150 $\Omega$                       | 60  |

| 4.41 | Line-to-neutral voltage ( $V_{LN}$ ) waveform for R=150 $\Omega$                | 61  |

| 4.42 | Line-to-neutral voltage (VLN) FFT waveform for $R=150\Omega$                    | 61  |

| 4.43 | Line-to-line voltage ( $V_{LL}$ ) waveform for R=150 $\Omega$                   | 61  |

| 4.44 | Line-to-line voltage ( $V_{LL}$ ) FFT waveform for R=150 $\Omega$               | 62  |

| 4.45 | Line current ( $I_L$ ) waveform for R=150 $\Omega$                              | 62  |

| 4.46 | Line current (I <sub>L</sub> ) FFT waveform for $R=150\Omega$                   | 63  |

| 4.47 | Line-to-neutral voltage ( $V_{LN}$ ) output waveform for R=100 $\Omega$ and     | 64  |

| 1 10 | L=10mH                                                                          | 64  |

| 4.48 | Line-to-line voltage ( $V_{LL}$ ) output waveform for R=100 $\Omega$ and L=10mH | 64  |

| 4.49 | Output line current (I <sub>L</sub> ) waveform for R=100 $\Omega$ and L= 10mH   | 65  |

| 4.50 | Line-to-neutral voltage ( $V_{LN}$ ) waveform for R=100 $\Omega$ and L=10mH     | 65  |

| 4.51 | Line-to-neutral voltage ( $V_{LN}$ ) FFT waveform for R=100 $\Omega$ and        | 66  |

|      | L=10mH                                                                          |     |

| 4.52 | Line-to-line voltage ( $V_{LL}$ ) waveform for R=100 $\Omega$ and L=10mH        | 66  |

| 4.53 | Line-to-line voltage ( $V_{LL}$ ) FFT waveform for R=100 $\Omega$ and L=10mH    | 67  |

| 4.54 | Line current (I <sub>L</sub> ) waveform for R=100 $\Omega$ and L=10mH           | 67  |

| 4.55 | Line current (I <sub>L</sub> ) FFT waveform for $R=100\Omega$ and $L=10mH$      | 68  |

| 4.56 | Voltage line-to-neutral ( $V_{LN}$ ) output waveform for R=100 $\Omega$ and     | 69  |

|      | L=30mH                                                                          | ••• |

| 4.57 | Line-to-line voltage (V <sub>LL</sub> ) output waveform for R=100 $\Omega$ and  | 69  |

|      | L=30mH                                                                          |     |

| 4.58 | Output line current (I <sub>L</sub> ) waveform for R=100 $\Omega$ and L= 30mH   | 70  |

| 4.59 | Line-to-neutral voltage ( $V_{LN}$ ) waveform for R=100 $\Omega$ and L=30mH     | 70  |

|      |                                                                                 |     |

| 4.60 | Line-to-neutral voltage (V <sub>LN</sub> ) FFT waveform for R=100 $\Omega$ and L=30mH | 71 |

|------|---------------------------------------------------------------------------------------|----|

| 4.61 | Line-to-line voltage ( $V_{LL}$ ) waveform for R=100 $\Omega$ and L=30mH              | 71 |

| 4.62 | Line-to-line voltage ( $V_{LL}$ ) FFT waveform for R=100 $\Omega$ and L=30mH          | 72 |

| 4.63 | Line current (I <sub>L</sub> ) waveform for R=100 $\Omega$ and L=30mH                 | 72 |

| 4.64 | Line current (I <sub>L</sub> ) FFT waveform for $R=100\Omega$ and $L=30mH$            | 73 |

| 4.65 | Line-to-neutral voltage ( $V_{LN}$ ) output waveform for R=100 $\Omega$ and           | 74 |

|      | L=50mH                                                                                |    |

| 4.66 | Line-to-line voltage (V <sub>LL</sub> ) output waveform for R=100 $\Omega$ and L=50mH | 74 |

| 4.67 | Output line current (I <sub>L</sub> ) waveform for $R=100\Omega$ and $L=50mH$         | 75 |

| 4.68 | Line-to-neutral voltage ( $V_{LN}$ ) waveform for R=100 $\Omega$ and L=50mH           | 75 |

| 4.69 | Line-to-neutral voltage ( $V_{LN}$ ) FFT waveform for R=100 $\Omega$ and L=50mH       | 76 |

| 4.70 | Line-to-line voltage ( $V_{LL}$ ) waveform for R=100 $\Omega$ and L=50mH              | 76 |

| 4.71 | Line-to-line voltage ( $V_{LL}$ ) FFT waveform for R=100 $\Omega$ and L=50mH          | 77 |

| 4.72 | Line current (I <sub>L</sub> ) waveform for $R=100\Omega$ and $L=50mH$                | 77 |

| 4.73 | Line current (I <sub>L</sub> ) FFT waveform for $R = 100\Omega$ and L=50mH            | 78 |

| 4.74 | Illustration of GMA for seven-level NPCMI                                             | 79 |

| 4.75 | Switching angle for positive region switches                                          | 80 |

| 4.76 | Switching angle for negative region switches                                          | 80 |

| 4.77 | Line-to-neutral voltage (V <sub>LN</sub> ) output waveform for resistive load         | 81 |

| 4.78 | Line-to-line voltage (V <sub>LL</sub> ) output waveform for resistive load            | 81 |

| 4.79 | Line current (I <sub>L</sub> ) output waveform for resistive load                     | 82 |

| 4.80 | Line-to-neutral voltage (V <sub>LN</sub> ) waveform for seven-level NPCMI             | 82 |

| 4.81 | Line-to-neutral voltage (V <sub>LN</sub> ) FFT waveform for seven-level NPCMI         | 83 |

| 4.82 | Line-to-line voltage (V <sub>LL</sub> ) waveform for seven-level NPCMI                | 83 |

| 4.83 | Line-to-line voltage (V <sub>LL</sub> ) FFT waveform for seven-level NPCMI            | 83 |

| 4.84 | Line current (I <sub>L</sub> ) waveform for seven-level NPCMI                         | 84 |

| 4.85 | Line current (I <sub>L</sub> ) FFT waveform for seven-level NPCMI                     | 84 |

| 4.86 | Line-to-neutral voltage (V <sub>LN</sub> ) output waveform for 100Hz                  | 87 |

| 4.87 | Line-to-line voltage (V <sub>LL</sub> ) output waveform for 100Hz                     | 87 |

| 4.88 | Line-to-neutral voltage ( $V_{LN}$ ) output waveform for 300Hz                        | 88 |

| 4.89 | Line-to-line voltage (V <sub>LL</sub> ) output waveform for 300Hz                     | 88 |

| 4.90 | Line-to-neutral voltage ( $V_{LN}$ ) output waveform for 500Hz                        | 89 |

| 4.91 | Line-to-line voltage ( $V_{LL}$ ) output waveform for 500Hz                           | 89 |

| 4.92 | THD (%) for resistive load, $R=100\Omega$                                             | 91 |

| 4.93 | THD (%) for resistive inductive load, $R=100\Omega$ , $L=30mH$                        | 91 |

| 4.94 | Line-to-neutral voltage ( $V_{LN}$ ) output waveform for 1000Hz                       | 92 |

| 4.95 | Line-to-line voltage ( $V_{LL}$ ) output waveform for 1000Hz                          | 93 |

|      |                                                                                       |    |

# LIST OF ABBREVIATIONS

| AC                      | Alternating Current                                             |

|-------------------------|-----------------------------------------------------------------|

| APODPWM                 | Alternative Phase Opposition Disposition Pulse Width Modulation |

| CCMLI                   | Cascaded Cell Multilevel Inverter                               |

| DC                      | Direct Current                                                  |

| DCMLI                   | Diode Clamped Multilevel Inverter                               |

| DTC                     | Direct Torque Control                                           |

| EMI                     | Electromagnetic Interference                                    |

| ESWM                    | Equal Step Width Method                                         |

| EV                      | Electric Vehicle                                                |

| FCMI                    | Flying Capacitor Multilevel Inverter                            |

| FFT                     | Fast Fourier Transform                                          |

| HV                      | High Voltage                                                    |

| HVDC                    | High Voltage Direct Current                                     |

| GMA                     | Graphical Method Analysis                                       |

| IEEE                    | Institute of Electrical and Electronics Engineering             |

| IGBT                    | Insulated Gate Bipolar Thyristor                                |

| ICDI                    | Line Current                                                    |

| MI                      | Multilevel Inverter                                             |

| MSWM                    | Modified Step Width Modulation                                  |

| MV                      | Medium Voltage                                                  |

| NPCMI                   | Neutral-Point-Clamped Multilevel Inverter                       |

| PBA                     | Penyonsang Berbilang Aras                                       |

| PDPWM                   | Phase Disposition Pulse Width Modulation                        |

| PODPWM                  | Phase Opposition Disposition Pulse Width Modulation             |

| PWM                     | Pulse Width Modulation                                          |

| R                       | Resistive                                                       |

| RL                      | Resistive Inductive                                             |

| SHE                     | Selective Harmonics Elimination                                 |

| SVM                     | Space Vector Modulation                                         |

| SPWM                    | Sinusoidal Pulse Width Modulation                               |

| SVPWM                   | Space Vector Pulse Width Modulation                             |

| TCHB                    | Transistor Clamped H-Bridge                                     |

| THD                     | Total Harmonics Distortion                                      |

| VDC                     | Voltage Direct Current                                          |

| UPFC                    | Unified Power Flow Controller                                   |

| V <sub>LN</sub>         | Line-to-neutral Voltage                                         |

| V LN<br>V <sub>LL</sub> | Line-to-line Voltage                                            |

| VSI                     | Voltage Source Inverter                                         |

| 101                     | voltage Source inverter                                         |

|                         |                                                                 |

# LIST OF SYMBOL

- $_{\circ}^{\Omega}$

- ohm degree omega micro angle ω

- μ

- α

#### **CHAPTER 1**

#### **INTRODUCTION**

#### 1.1 Background

Today, the utilisation of multilevel inverters (MI) has become wider when compared to the existing two-level voltage source inverters (VSI) in the power industry especially in high voltage and high power applications. This type of multilevel inverter offers high efficiency and reduced production costs which are greatly desired in the industry. Generally, the multilevel inverter operates by synthesising a desired output voltage from several levels of DC voltages or DC supplies. At low voltage, the conventional twolevel VSI are sufficient. However, the situation changes when it comes to medium voltage (MV) and high voltage (HV). By using a multilevel inverter, more than two levels of the output voltage can be achieved with a smoother and less distorted waveform with a low Total Harmonics Distortion (THD) value [1]. A desired output voltage waveform can be collectively obtained from a MI with the desirable features of less distortion, low switching frequency, higher efficiency, and lower voltage devices.

The uniqueness of the MI structure allows it to be operated at higher voltages without the use of a power transformer. As the number of the MI level increases, the harmonic content of the output voltage waveform decreases significantly [2 and 3]. There are three main topologies for MI; neutral-point-clamped, flying capacitor [4] and H-bridge cascaded [5, 6, 7 and 8]. These topologies are classified by the structures that are used in each construction. Each topology offers its own advantages and disadvantages which make it different in aspects of application.

Among these three topologies, the Neutral-Point-Clamped Multilevel Inverter (NPCMI) is the most widely used in all areas of industry. This topology was first proposed by A. Nabae, I. Takashi and H. Akagi [9]. Basically, NPCMI operates by producing a small step of staircase output voltage from several levels of DC capacitor voltages and can be extended to a higher level so that it is able to reach a higher AC voltage output. Therefore NPCMI can be constructed to produce a greater amount of smaller voltage steps that in the end will be similar to a sinusoidal waveform.

As harmonics are one of the issues in power quality that usually occurs in a power system network, the need to reduce harmonics is significant. In a standard Alternating Current (AC) power system, the harmonics occur at a multiple of the fundamental frequency which is either at a fundamental frequency of 50 Hz or 60 Hz. Harmonic distortion can be found both in voltage and current waveforms which is caused by electronic component loads or in common wiring systems according to Ohm's Law. THD can be defined as a ratio of the sum (as a percentage) of all harmonic components to the fundamental frequency component. As applied to a power system, a lower THD means a reduction of harmonics to the lowest percentage.

#### **1.2 Problem Statement**

In previous years, MI has been used as a replacement for conventional VSI, whether it is in a power system or in machinery applications. In a low voltage application, there is nothing of concern if the conventional VSI is employed. However, this is not the case when VSI is used in medium or high power applications. Even though many research studies have been conducted in this area, there is still some rooms for improvement. One of the improvements of interest to researchers is to obtain an output voltage with lower THD values. A result from previous work (Chaturvedi, Jain and Agrawal, 2005, Zambra et al., 2008, Panagis et al., 2008 and Mailah et al., 2009) showed that the values of the output voltage THD are higher compared to the value stated by the IEEE STD 519-1992 by using different method of finding switching angle [10, 11, 12 and 13]. According to the *IEEE* standard, the number of levels of a multilevel inverter should be increased in order to obtain an output waveform similar to a sinusoidal waveform so that the THD is reduced. The standard mentioned 5 % as the limit for the THD value [14]. Previously, the existing method to calculate the switching angle like space vector modulation (SVM), pulse width modulation (PWM) and others are complicated method to determine approximate switching angle that give low THD.

The motivation for this current work is to obtain an output voltage waveform with a low THD value. This is to be achieved through the determination of the switching angle of the power electronic devices by proposing a new technique of predicting the switching angle. The research topic is important as it provides an alternative and simpler method of calculating the switching angle that can produce an output voltage waveform with a smaller THD compared to the existing methods which are more complicated in order to determine the switching angle.

Another motivation is that based on previous work by Sayago *et al.*, one of the less attractive features of NPCMI is its relatively high switching losses which limit the switching frequency up to 1050 Hertz [15]. So in this work, the designed NPCMI is simulated under various switching frequencies ranging from 50 Hz to 1000 Hz to analyse the stability of this NPCMI when subjected to changes in switching frequency.

#### **1.3** Aim and Objectives

The aim of this work is to propose a new method to determine suitable switching angle called Graphical Method Analysis (GMA) in order to achieve a lower THD output voltage value.

There are three main objectives of this research. These objectives are listed as follows:

- 1. To model a simulation circuit of a three-phase five-level NPCMI using the Matlab/Simulink simulation software.

- 2. To propose and test the performance of GMA used in determining the switching angle of three phase five-level NPCMI and analyze the harmonics contents of the output voltage.

3. To investigate the stability of a three-phase five-level NPCMI when subjected to varying switching frequencies.

#### 1.4 Scope of Work

Based on the previous work of a three-phase three-level NPCMI [13], this work is expanded to design and model a three-phase five-level NPCMI using the Matlab/Simulink simulation software. The main aim of this work focuses on a simulation model to determine the switching angle using the new proposed method. It begins with the design of a three-phase five-level NPCMI and then calculates and determines the switching angle of each power electronic switch parameter. Graphical Method Analysis (GMA) is proposed and applied in this work. The calculated switching angles are applied and the associated THD of the output voltage waveforms are noted. The total harmonic distortion (THD) is observed at each step while running the simulation. The THD value obtained from this work is compared to other works related to this design. Subsequently a higher level is constructed to prove the proposed method is useable to achieve the best output waveform. The switching frequency is varied from 50 Hz to 1000 Hz and the THD is observed to determine the stability of the proposed system.

#### 1.5 Contributions

The contributions of this work are:

- 1. Graphical Method Analysis (GMA) has been proposed in this work for a three-phase NPCMI and has been simulated and validated using Matlab/Simulink simulation software. This method can be used to obtain the best output waveform to achieve a lower THD value compared to other existing methods.

- 2. The stability of the NPCMI has been analysed and shown to be stable for a switching frequency ranging from 50 Hz to 1000 Hz.

### 1.6 Thesis Layout

This thesis is organised in five chapters. Chapter 1 introduces the background of the project, gives the problem statement, scope of works and the aims and objectives of the research. The contributions of this work are also stated.

Chapter 2 presents a literature review related to the study. It begins with a discussion on MI focusing on NPCMI and also a few reviews of other topologies, control strategies, THD, applications of MI and a conclusion of the literature review. Several research works concerning published results are also considered as a reference in developing the proposed graphical method for a three-phase NPCMI.

Chapter 3 explains the research methodology that is used to obtain the results from this project. First of all, the basic principles and structure of this three-phase five-level

NPCMI are explained. Then the modelling of the three-phase five-level NPCMI is constructed by using the Matlab/Simulink software. Furthermore, the GMA of this structure is created to provide a comparison with the results of other research works. Then, the method is expanded to a three phase seven-level NPCMI. Finally, the design of the NPCMI is simulated under varying switching frequencies in order to investigate the performance and stability.

Chapter 4 presents the results of this work. Firstly, the results of the construction and calculation of the graphical method analysis (GMA) of the three-phase five-level NPCMI are shown, analysed and discussed. The total harmonic distortion of the output voltage waveform of this structure is observed and compared to previous work to ensure that this research has improved the situation. Then the three-phase seven-level NPCMI results using the same graphical method analysis technique are analysed to prove that a higher level of NPCMI will produce a better output and the proposed method is valid. The switching frequency is varied to observe the stability of the system. All results obtained are discussed and described.

Finally, Chapter 5 concludes the overall research of the construction and analysis result of this three-phase five-level NPCMI. This chapter also includes a few recommendations that can be implemented in this research area in the future.

#### REFERENCES

- [1] Peng, F. Z. (2000). A Generalized Multilevel Inverter Topology with Self Voltage Balancing. *IEEE Industry Applications Conference 2000*, Rome, Italy, Volume 3, 8-12 October 2000, pp. 2024-2031.

- [2] Bhagwat, P. M. and Stefanovic, V. R. (1983). Generalized Structure of a PWM Inverter. *IEEE Transaction on Industry Applications*, Volume 19, No. 6, November/December 1983, pp. 1057-1069.

- [3] Carpita, M. and Teconi, S. (1991). A Novel Multilevel Structure for Voltage Source Inverter. *Proceeding European Power Electronics*, 1991, pp. 90-94.

- [4] Meynard, T. A. and Foch, H. (1992). Multi-level Choppers For High Voltage Applications. *Proceeding European Conf. Power Electronics and Applications*, 1992, pp. 45-50.

- [5] Peng, F. Z., Lai, J. S., McKeever, J. W., and VanCOevering, J. (1996). A Multilevel Voltage-Source Inverter with Separate DC Sources for Static Var Generation," *IEEE Transactions on Industry Applications*, Volume 32, No. 5, September/October 1996, pp. 1130-1 138.

- [6] Peng, F. Z., Lai, J. S., McKeever, J., and Vancoevering, J. (1995). A Multilevel Voltage-Source Converter System with Balanced DC Voltages. *IEEEPESC 1995*, Atlanta, Georgia, USA, pp. 1 144-1 150.

- [7] Rodriguez, J., Bernet, S., Wu, B., Pontt, J. O., and Kouro, S. (2007). Multilevel Voltage-Source Converter Topologies for Industrial medium-voltage drives," IEEE Trans. Ind. Electron., vol. 54, no. 6, Dec. 2007, pp. 2930–2945.

- [8] Rodriguez, J., Lai, J. S., and Peng F. Z. (2002). Multilevel inverters: A survey of topologies, controls, and applications," *IEEE Transaction Ind. Electron*, Volume 49, no. 4, Aug. 2002, pp. 724–738.

- [9] Nabae, A., Takahashi, I., and Akagi, H. (1981). A New Neutral-Point-Clamped PWM Inverter. *IEEE Transaction Ind. Application*, Vol 1A-17, sept/oct. 1981, pp 518-523.

- [10] Chaturvedi,, P., Jain, S. and Agrawat, P. (2005). Modeling, Simulation and Analysis of Three-Level Neutral Point Clamped Inverter Using Matlab/Simulink/Power System Blockset. *Proceeding of the 8<sup>th</sup> International Conference on Electrical Machines and System 2005*, Nanjing, China, Volume 2, pp. 1223-1227.

- [11] Zambra, D. A. B., Rech, C., Goncalves, F. A. S. and Pinheiro J. R. (2008). Power Losses Analysis and Cooling System Design of Three Topologies of Multilevel Inverters." *IEEE Power Electronics Specialists Conference 2008*, 15-19 June 2008, pp. 4290-4295.

- [12] Panagis, P., Stergioupolos, A., Marabeas, P. and Manias, S. (2008). Comparison of State of the Art Multilevel Inverters. *IEEE Power Electronics Specialist Conference 2008*, 15-19 June 2008, pp 4296-4301.

- [13] Mailah, N. F., Bashi, S. M., Aris, I. and Mariun, N. (2009). Neutral-Point-Clamped Multilevel Inverter Using Space Vector Modulation. *European Journal of Scientific Research*, Volume 28, no 1, pp. 82-91, 2009.

- [14] Blooming, T. M and Carnovale, D. J. (2006). Application of IEEE STD 512-1992 Harmonic Limits. *Conference Record of the 2006 IEEE IAS Pulp and Paper Conference*, 2006.

- [15] Sayago, J., Brückner, T., and Bernet, S. (2008). How to Select the System Voltage of MV Drives - A Comparison of Semiconductor Expenses. *IEEE Trans. Ind. Electro.*, Volume 55, No. 9, Sep. 2008, pp. 3381–3390.

- [16] Lai, J. S. and Peng, F. Z. (1996). Multilevel Converters A New Breed of Power Converters. *IEEE Transactions on Industry*, Volume 32, No. 3, May/June 1996, pp. 509-517.

- [17] Tolbert, L. M., Peng, F. Z., and Habetler, T. G. (1999). Multilevel Converters for Large Electric Drives. *IEEE Transaction Ind. Application*, Volume 35, no. 1, Jan./Feb. 1999, pp. 36–44.

- [18] Sangsun, K., Todorovic, M. H., and Enjeti, P. N. (2003). Three-phase Active Harmonic Rectifier (AHR) to Improve Utility Input Current THD in Telecommunication Power Distribution System. *IEEE Transaction Ind. Application* Volume 39, no. 4, Jul./Aug. 2003, pp. 1143–1150.

- [19] Khomfoi, S. and Praisuwanna, N. (2010). A Hybrid Cascaded Multilevel Inverter for Interfacing with Renewable Energy Resources. *The 2010 International Power Electronics Conference*, pp. 2912-2917, 2010.

- [20] Rashid, M. H. (2001). Power Electronics: Circuits, Devices and Applications. New Jersey: Prentice Hall, 2001.

- [21] Brückner, T. and Bernet, S. (2001). Loss Balancing in Three-level Voltage Source Inverters Applying Active NPC Switches. *Proceeding IEEE Power Electron. Spec. Conference*, Vancouver, BC, Canada, 2001, pp. 1135–1140.

- [22] Brückner, T., Bernet, S., and Güldner, H. (2005). The Active NPC Converter and its Loss-Balancing Control. *IEEE Trans. Ind. Electron*, Volume. 52, no. 3, Jun. 2005, pp. 855–868.

- [23] Brückner,, T., Bernet S., and Steimer, P. K. (2007). Feedforward Loss Control of Three-level Active NPC Converters. *IEEE Trans. Ind. Applications*, Volume 43, no. 6, Nov./Dec. 2007, pp. 1588–1596.

- [24] Bernet, S. (2000). Recent Developments of High Power Converters for Industry and Traction Applications. *IEEE Trans. Power Electron*, Volume 15, No. 6, Nov. 2000, pp. 1102–1117.

- [25] Steimer, P. K., Apeldoorn, O., Ødegård, B., Bernet, S., and Brückner, T. (2005).

Very High Power IGCT PEBB Technology. *IEEE Power Electron. Spec. Conference*, Recife, Brazil, 2005, pp. 1–7.

- [26] Rodriguez, J., Bernet, S., Wu, B., Steimer, P. K., and Lizama, I. E. (2010). A Survey on Neutral-Point-Clamped Inverters. *IEEE Transactions on Industrial Electronics 2010*. Volume 57, N 7, July 2010.

- [27] Purkait, P. and Srikanth, R. S. (2006). A Simple SVPWM Algorithm For Elimination of Neutral Point Current in Multi Level Inverter. *International Symposium on Power Electronics, Electrical Drives, Automation and Motion*, 2006.

- [28] Leon, J. I., Vazquez, S., Portillo, R., Franquelo L. G., Carrasco, J. M., Wheeler, P. W., and Watson, A. J. (2009). Three-dimensional Feed Forward Space Vector Modulation Applied to Multilevel Diode-clamped Converters. *IEEE Transaction Ind. Electron.*, Volume 56, no. 1, Jan. 2009, pp. 101–109.

- [29] Gupta, A. K. and Khambadkone, A. M. (2006). A Space Vector PWM Scheme for Multilevel Inverters Based on Two-level Space Vector PWM. *IEEE Trans. Ind. Electron.*, Volume 53, no. 5, Oct. 2006, pp. 1631–1639.

- [30] Gupta, A. K. and Khambadkone, A. M. (2007). A Simple Space Vector PWM Scheme to Operate a Three-level NPC Inverter at High Modulation Index Including Overmodulation Region with Neutral Point Balancing. *IEEE Transaction Ind. Appl.*, Volume 43, no. 3, May/Jun. 2007, pp. 751–760.

- [31] Hu,, H., Yao, W., and Lu, Z. (2007). Design and Implementation of Three-level Space Vector PWM IP Core for FPGAs. *IEEE Transaction. Power Electron*, Volume 22, no. 6, Nov. 2007, pp. 2234–2244.

- [32] Lopez, O., Alvarez, J., Doval-Gandoy, J., Freijedo F. D., Nogueiras, A., Lago, A. and Penalver, C. M. (2008). Comparison of the FPGA Implementation of Two Multilevel Space Vector PWM Algorithms. *IEEE Transaction Ind. Electron*, Volume 55, no. 4, Apr. 2008, pp. 1537–1547.

- [33] Busquets-Monge, S., Ortega, J. D., Bordonau, J., Beristain, J. A., and Rocabert J. (2008). Closed-loop Control of a Three-Phase Neutral-Point-Clamped Inverter Using an Optimized Virtual-Vector-Based Pulse Width Modulation. *IEEE Trans. Ind. Electron*, Volume 55, no. 5, May 2008, pp. 2061–2071.

- [34] Pan, Z., Peng, F. Z., Stefanovic, V. and Leuthen, M. (2004). A Diode-Clamped Multilevel Converter with Reduced Number of Clamping Diodes. *IEEE Transaction 2004.*

- [35] Kim, J. H., Sul, S. K., and Enjeti, P. N. (2008). A Carrier-Based PWM Method with Optimal Switching Sequence for a Multilevel Four-leg Voltage-source Inverter. *IEEE Transaction Ind. Appl.*, Volume 44, no. 4, Jul./Aug. 2008, pp. 1239–1248.

- [36] Ben-Brahim, L. and Tadakuma, S. (2006). A Novel Multilevel Carrier-Based PWM-Control Method for GTO Inverter in Low Index Modulation Region. *IEEE Trans. Ind. App*, Volume 42, No. 1, Jan/Feb. 2006, pp. 121–127.

- [37] Loh, P. C., Blaabjerg, F., and Wong, C. P. (2007). Comparative Evaluation of Pulse Width Modulation Strategies for Z-source Neutral-Point-Clamped Inverter. *IEEE Trans. Power Electron*, Volume 22, no. 3, May 2007, pp. 1005–1013.

- [38] Loh, P. C., Blaabjerg, F., Gao, F., Baby, A. and Tan, D. A. C. (2008). Pulsewidth Modulation of Neutral-Point-Clamped Indirect Matrix Converter. *IEEE Transaction Ind. Appl.*, Volume 44, no. 6, Nov./Dec. 2008, pp. 1805– 1814.

- [39] Videt, A., Le Moigne, Idir, P., Baudesson, P., and Cimetiere, X. (2007). A New Carrier-Based PWM Providing Common-Mode-Current Reduction and DC-Bus Balancing for Three-level Inverters. *IEEE Transaction Ind. Electron*, Volume 54, no. 6, Dec. 2007, pp. 3001–3011.

- [40] Franquelo, L. G., Napoles,, J., Guisado, R. C. P., Leon, J. I., and Aguirre, M. A. (2007). A Flexible Selective Harmonic Mitigation Technique to Meet Grid Codes in Three-level PWM Converters. *IEEE Trans. Ind. Electron.*, Volume 54, no. 6, Dec. 2007, pp. 3022–3029.

- [41] Patel, H. S. and Hoft, R. G. (1973). Generalized Techniques of Harmonic Elimination and Voltage Control in Thyristor Inverters: Part I—Harmonic Elimination. *IEEE Transaction Ind. Appl.* Volume IA-9, no. 3, May 1973, pp. 310–317.

- [42] Sirisukprasert, S., Lai, J. S., and Liu, T. H. (2002). Optimum Harmonic Reduction With a Wide Range of Modulation Indexes for Multilevel Converters. *IEEE Transaction Ind. Electron*, Volume 49, no. 4, Aug. 2002, pp. 875–881.

- [43] Sahali, Y. and Fellah M. K. (2005). Comparison Between Optimal Minimization of Total Harmonic Distortion and Harmonic Elimination with Voltage Control Candidates for Multilevel Inverters. *Journal of Electrical Systems*, 1-3, 2005, pp. 32-46.

- [44] Yousefpoor, N. and Fathi, S. H. (2012). THD Minimization Applied Directly on the Line-to-Line Voltage of Multilevel Inverters. *IEEE Transaction On Industrial Electronics*, Volume 59, no.1, Jan 2012.

- [45] Du, Z. and Tolbert, L. M. (2006). Active Harmonic Elimination for Multilevel Converters. *IEEE Transaction on Power Electronics*, Volume 21, no. 2, March 2006.

- [46] Wanjekeche, T., Nicolae, D.V. and Jimoh, A.A. (2009). A Cascaded NPC/H-Bridge Inverter with Simplified Control Strategy and Minimum Component Count. *IEEE AFRICON 2009*, Nairobi, Kenya. 23 - 25 September 2009.

- [47] Singh, P., and Tiwari, S., and Gupta, KK. (2012). A New Topology of Transistor Clamped 5-Level H-Bridge Multilevel Inverter with voltage Boosting Capacity," *IEEE International Conference on Power Electronics, Drives and Energy Systems*, December16-19, 2012, Bengaluru, India.

- [48] Rao, G. S. and Sekhar, K. C. (2012). A Novel Five-Level SPWM Inverter System for Dual-Fed Induction Motor Drive." *IEEE International Conference on Advanced Communication Control and Computing Technologies (ICACCCT)*, 2012.

- [49] Palanivel, P. and Dash, S. S. (2011). Analysis of THD and Output Voltage Performance for Cascaded Multilevel Inverter Using Carrier Pulse Width Modulation Techniques." *IET Power Electron.*, 2011, Volume 4, Iss. 8, pp. 951– 958.

- [50] Manimala, V. Geetha, M. E. and Renuga, P. (2011). Design and Simulation of Five-level Cascaded Inverter Using Multilevel Sinusoidal Pulse Width Modulation Strategies. *IEEE Transaction on Power Electronics*, 2011, pp. 280-283.

- [51] Lakshmi, T. V. V. S., George, N., Umashankar, S., and Kothari, D. P. (2013). Cascaded Seven Level Inverter with Reduced Number of Switches Using Level Shifting PWM Technique. *International Conference on Power, Energy and Control (ICPEC) 2013*, 6-8 February 2013, pp. 676-680.

- [52] Gabriel, O. H. P., Maswood, A, I., and Venkataraman, A. (2012). Multiple-Poles Multilevel Diode-Clamped Inverter (M2DCI) Topology for Alternative Multilevel Converter. *International Power and Energy Conference (IPEC) 2012*, 12-13 December 2012.

- [53] Shukla, A., Ghosh A., and Joshi A. (2007). Multilevel Converters for Unified Power Flow Controller: A Performance Based Analysis. *IEEE Power Engineering Society General Meeting 2007*, Tampa, USA, 24-28 June 2007, pp. 1-8.

- [54] Sekhar, K. C. and Das, G. T. R. (2006). Five-level SPWM Inverter for an Induction Motor with Open-end Windings. *First International Power and Energy Coference PECon 2006*, November 28-29, 2006, Putrajaya, Malaysia.

- [55] Kouro, S., Bernal, R., Miranda, H., Silva, C. A.,and Rodríguez, J. (2007). High Performance Torque and Flux Control for Multilevel Inverter Fed Induction Motors." *IEEE Transaction on Power Electronics*, Volume 22, no. 6, November 2007.

- [56] Khoucha, F., Lagoun, S. M., Marouani, K., Kheloui, A., and Hachemi, M. E. B. (2010). Hybrid Cascaded H-Bridge Multilevel-Inverter Induction-Motor-Drive Direct Torque Control for Automotive Applications. *IEEE transactions on industrial electronics*, Volume 57, no. 3, March 2010, pp. 892-899.

- [57] Pravin, S. E. and Starbel, R. N. (2011). Induction Motor Drive Using Seven Level Multilevel Inverter for Energy Saving in Variable Torque Load Application. International Conference on Computer, Communication and Electrical Technology – ICCCET 2011, 18th & 19th March, 2011.

- [58] Private communication with Associate Professor Dr. S. M. Bashi.

### APPENDICES

### A: Parameters for each devices:

1. Filter, L

| Block Param        |                                                                                         |       |

|--------------------|-----------------------------------------------------------------------------------------|-------|

| -Parallel RLC Bran |                                                                                         |       |

|                    | allel branch of RLC elements.<br>ype' parameter to add or remove elements from the bran | ch.   |

| Parameters         |                                                                                         |       |

| Branch type: 📘     |                                                                                         | ~     |

| Inductance L (H)   | :                                                                                       |       |

| 100e-3             |                                                                                         |       |

| 📃 Set the initial  | inductor current                                                                        |       |

| Measurements       | None                                                                                    | ~     |

|                    |                                                                                         |       |

|                    |                                                                                         |       |

|                    | OK Cancel Help                                                                          | Apply |

| capacitor          |                                                                                         |       |

2. DC capacitor

| 🐱 Block Para      | meters: C1                                                                                     |       |

|-------------------|------------------------------------------------------------------------------------------------|-------|

| -Parallel RLC Bra | anch (mask) (link)                                                                             |       |

|                   | arallel branch of RLC elements.<br>h type' parameter to add or remove elements from the branch | ٦.    |

| Parameters        |                                                                                                |       |

| Branch type:      | c                                                                                              | ~     |

| Capacitance C     | (F):                                                                                           |       |

| 2200e-6           |                                                                                                |       |

| 📃 Set the initi   | ial capacitor voltage                                                                          |       |

| Measurements      | None                                                                                           | ~     |

|                   |                                                                                                |       |

|                   |                                                                                                |       |

|                   | OK Cancel Help A                                                                               | Apply |

# 3. Diode Clamped

| Diode (mask) (link)         Implements a diode in parallel with a series RC snubber circuit.         In on-state the Diode model has an internal resistance (Ron) and inductance (Lon).         For most applications the internal inductance should be set to zero.         The Diode impedance is infinite in off-state mode.         Parameters         Resistance Ron (Ohms) :         0.001         Inductance Lon (H) :         0         Forward voltage Vf (V) :         0.7         Initial current Ic (A) :         0         Snubber resistance Cs (F) :         0         Snubber capacitance Cs (F) :         0         Show measurement port | 🐱 Bl           | ock Parameters: DC1 🛛 🔀                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| In on-state the Diode model has an internal resistance (Ron) and inductance (Lon).<br>For most applications the internal inductance should be set to zero.<br>The Diode impedance is infinite in off-state mode.<br>Parameters<br>Resistance Ron (Ohms) :<br>0.001  <br>Inductance Lon (H) :<br>0<br>Forward voltage Vf (V) :<br>0.7<br>Initial current Ic (A) :<br>0<br>Snubber resistance Rs (Ohms) :<br>inf<br>Snubber capacitance Cs (F) :<br>0<br>Show measurement port                                                                                                                                                                               | Diod           | e (mask) (link)                                                                                                                                    |

| Resistance Ron (Ohms) :   0.001   Inductance Lon (H) :   0   Forward voltage Vf (V) :   0.7   Initial current Ic (A) :   0   Snubber resistance Rs (Ohms) :   inf   Snubber capacitance Cs (F) :   0                                                                                                                                                                                                                                                                                                                                                                                                                                                       | In or<br>For n | n-state the Diode model has an internal resistance (Ron) and inductance (Lon).<br>Most applications the internal inductance should be set to zero. |

| 0.001   Inductance Lon (H) :   0   Forward voltage Vf (V) :   0.7   Initial current Ic (A) :   0   Snubber resistance Rs (Ohms) :   inf   Snubber capacitance Cs (F) :   0   Show measurement port                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Para           | meters                                                                                                                                             |

| Inductance Lon (H) :<br>0<br>Forward voltage Vf (V) :<br>0.7<br>Initial current Ic (A) :<br>0<br>Snubber resistance Rs (Ohms) :<br>inf<br>Snubber capacitance Cs (F) :<br>0<br>Snubber capacitance Cs (F) :                                                                                                                                                                                                                                                                                                                                                                                                                                                | Resi           | stance Ron (Ohms) :                                                                                                                                |

| 0   Forward voltage Vf (V) :   0.7   Initial current Ic (A) :   0   Snubber resistance Rs (Ohms) :   inf   Snubber capacitance Cs (F) :   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.0            | 01                                                                                                                                                 |

| Forward voltage Vf (V) :   0.7   Initial current Ic (A) :   0   Snubber resistance Rs (Ohms) :   inf   Snubber capacitance Cs (F) :   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Indu           | ictance Lon (H) :                                                                                                                                  |

| 0.7   Initial current Ic (A) :   0   Snubber resistance Rs (Ohms) :   inf   Snubber capacitance Cs (F) :   0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0              |                                                                                                                                                    |

| Initial current Ic (A) :  Initial current Ic (A) :  Snubber resistance Rs (Ohms) :  Inf Snubber capacitance Cs (F) :  Inf Snubber capacitance Cs (F) : Inf                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Forv           | vard voltage Vf (V) :                                                                                                                              |

| 0         Snubber resistance Rs (Ohms) :         inf         Snubber capacitance Cs (F) :         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.7            |                                                                                                                                                    |

| Snubber resistance Rs (Ohms) :<br>inf<br>Snubber capacitance Cs (F) :<br>0<br>Show measurement port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Initia         | al current Ic (A) :                                                                                                                                |

| inf Snubber capacitance Cs (F) : 0 Show measurement port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0              |                                                                                                                                                    |

| Snubber capacitance Cs (F) : 0 Show measurement port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Snut           | ober resistance Rs (Ohms) :                                                                                                                        |

| 0 Show measurement port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | inf            |                                                                                                                                                    |

| Show measurement port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Snut           | ober capacitance Cs (F) :                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0              |                                                                                                                                                    |

| OK Cancel Help Apply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2              | 5how measurement port                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | OK Cancel Help Apply                                                                                                                               |