# **UNIVERSITI PUTRA MALAYSIA**

DESIGN OF A LOW NOISE LOW POWER FRONT END READOUT CIRCUIT FOR NEUTRON DETECTION USING 130NM CMOS TECHNOLOGY

**NUERAIMAITI AIMAIER**

FK 2015 44

## DESIGN OF A LOW NOISE LOW POWER FRONT END READOUT CIRCUIT FOR NEUTRON DETECTION USING 130NM CMOS TECHNOLOGY

Thesis Submitted to the School of Graduate Studies, Universiti Putra Malaysia, in Fulfilment of the Requirements for the Degree of Master of Science

May 2015

All material contained within the thesis, including without limitation text, logos, icons, photographs and all other artwork, is copyright material of Universiti Putra Malaysia unless otherwise stated. Use may be made of any material contained within the thesis for non-commercial purposes from the copyright holder. Commercial use of material may only be made with the express, prior, written permission of Universiti Putra Malaysia.

Copyright © Universiti Putra Malaysia

Abstract of thesis presented to the Senate of Universiti Putra Malaysia in fulfilment of the requirement for the degree of Master of Science

### DESIGN OF A LOW NOISE LOW POWER FRONT END READOUT CIRCUIT FOR NEUTRON DETECTION USING 130NM CMOS TECHNOLOGY

By

#### NUERAIMAITI AIMAIER

#### May 2015

#### Chair: Roslina Mohd Sidek, Associate Professor, PhD

### **Faculty: Engineering**

Neutron detectors are used to detect neutron particles in science, security, and other applications. A typical neutron detection system consists of detector itself and frontend readout electronics. Since neutron detector does not have its operational setting in terms of signal speed and output signal gain, it requires a suitable readout electronics which capable of accepting wide range and fast input signal.

Front-end readout electronics designed in CMOS technology has enabled highly integrated readout channels which increases the resolution of neutron detection. However, due to technology down scaling and the requirements for low power design, the transistor operating region tends to shift from strong inversion to moderate inversion, and the classic MOSFET modelling, also known as "square law" is not applicable anymore. Hence, a more accurate MOSFET modelling is needed in deep submicron CMOS technology to design the front-end readout circuit. Another one significant challenge in designing front-end readout circuit is to design low noise while at the same time minimizing the power consumption. This study presents the design of a low noise and low power front-end readout circuit that is implemented in 130nm CMOS technology. The front-end readout system which has been designed in this study was composed of two parts: (a) pre - amplifier and (b) amplifier pulse shaper.

A simplified Enz Krummenacher Vittoz model or known as EKV model was studied and applied in this work. The model is quite successful in all CMOS operating region, especially in moderate inversion to predict the MOSFET behaviour. The input transistor of front-end system was carefully designed which is critical to readout channel noise performance. A p-channel MOSFET is selected for input transistor due to its lower flicker noise coefficient, and the geometries of all transistors in preamplifier are optimized for minimum noise contribution to the system. The input transistor is made to operate in moderate inversion which is good trade-off between system speed and power consumption. A folded cascode structure is designed for preamplifier to boost the gain and bandwidth. A first order pulse shaper with pole zero cancellation circuit is designed with short peaking time to meet fast counting rate requirements.

A series of simulation including post-layout simulation was carried out to measure front-end system equivalent noise charge, power consumption, charge gain, peaking time, high counting rate and linearity. Results showed that the front-end readout channel designed in CMOS technology in this work has a good electronic noise performance with only an equivalent noise charge of 183 electrons for a detector capacitance of 1pF. The channel power consumption is only about 0.89mW with a charge gain of 3.6mV/fC. Peaking time is around 104 nanoseconds and it is capable of accepting high count rate input signal of 333 kHz with less than 5% output signal distortion. These results showed that the designed front-end readout circuit implemented in 130nm CMOS technology with input transistor working in moderate inversion has good electronic noise performance, high counting rate while reducing the total power consumption. It also shows that the front-end readout system is suitable for using in neutron particle detection system.

Abstrak tesis yang dikemukakan kepada Senat Universiti Putra Malaysia Sebagai memenuhi keperluan untuk ijazah Master Sains

### REKA BENTUK LITAR PEMBACA BERHINGAR DAN BERKUASA RENDAH UNTUK PENGESAN NEUTRON MENGGUNAKAN TEKNOLOGI 130NM CMOS

Oleh

#### NUERAIMAITI AIMAIER

#### Mei 2015

#### Pengersui: Roslina Mohd Sidek, Profesor Madya, PhD

#### Fakulti: Kejuruteraan

Pengesan neutron digunakan bagi tujuan mengesan zarah neutron dalam bidang sains, keselamatan dan sebagainya. Secara amnya, sistem pengesanan zarah neutron adalah terdiri daripada pengesan neutron itu sendiri dan juga litar pembaca bahagian depan. Oleh sebab pengesan neutron tidak memiliki penetapan operasi dari segi kelajuan isyarat dan gandaan isyarat keluaran, ia memerlukan sistem pemproses elektronik yang sesuai dan mampu menerima isyarat kemasukan yang berjulat lebar dan pantas.

Rekabentuk litar pembaca bahagian depan dalam mod litar bersepadu dengan menggunakan teknologi CMOS membolehkan sistem pemproses elektronik direkabentuk pada skala yang besar serta dapat membantu meningkatkan resolusi pada sistem pengesanan neutron. Walau bagaimanapun, pengecilan skala serta keperluan bagi rekabentuk litar berkuasa rendah menyebabkan kawasan operasi bagi rekabentuk transistor yang akan digunakan beralih daripada penyongsangan kuat ke penyongsangan sederhana, ini menyebabkan pemodelan MOSFET klasik yang juga dikenali sebagai "square law" tidak lagi boleh digunakan. Oleh itu, pemodelan MOSFET yang lebih jitu amat diperlukan dalam teknologi CMOS submikron bagi rekabentuk sistem pemproses elektronik yang akan digunakan dalam litar pembaca bahagian depan. Satu lagi cabaran besar dalam reka bentuk litar pembaca bahagian depan ialah reka bentuk dengan hingar elektronik yang rendah tetapi pada masa masih mengekalkan penggunaan kuasa yang rendah. Kajian ini membentangkan satu rekabentuk sistem pemproses elektronik bagi sistem pengesanan neutron menggunakan teknologi 130nm CMOS. Ia direkabentuk dengan mengambil kira dua parameter penting iaitu; (a) hingar elektronik dan (b) penggunaan kuasa yang rendah.

Model Enz Krummenacher Vittoz yang dikenali sebagai model EKV yang dipermudahkan telah dikaji dan diaplikasi dalam kajian ini dan telah menunjukkan prestasi yang agak berjaya dalam semua CMOS kawasan operasi, terutama dalam penyongsangan sederhana, untuk meramalkan tingkah laku MOSFET. Bahagian transistor masukkan dalam litar pembaca bahagian depan ini telah direkabentuk dengan teliti kerana ia amat kritikal dalam menentukan prestasi hingar elektronik yang akan dijana oleh litar pembaca bahagian depan tersebut. Transistor MOSFET saluran-p telah dipilih sebagai transistor masukkan kerana ia mempunyai pekali hingar kerlipan yang lebih rendah berbanding transistor saluran-n. Geometri bagi semua transistor pada bahagian pra-amplifier telah dioptimakan bagi meminimakan hingar elektronik dalam sistem. Transistor masukkan juga direka supaya beroperasi pada rantau penyongsangan sederhana supaya satu keseimbangan yang baik antara

kelajuan sistem dan penggunaan kuasa dapat diperolehi. Struktur kaskod terlipat telah digunakan bagi rekbentuk bahagian pra-amplifier bagi meningkatkan gandaan dan lebar jalur. Litar pembentuk denyut tertib pertama dengan litar pembatal kutub-sifar telah direka dengan masa puncak yang singkat bagi memenuhi keperluan kadar pembilangan yang pantas.

Satu siri simulasi termasuk simulasi pasca-persediaan telah dilaksanakan bagi mengukur cas hingar setara, penggunaan kuasa, gandaan, masa puncak denyut, kadar pembilangan serta kelinearan sistem. Keputusan kajian menunjukkan bahawa litar pembaca bahagian depan yang direkabentuk dalam kajian ini mempunyai prestasi hingar elektronik yang baik dengan cas hingar setara 183 elektron untuk kemuatan pengesan 1pF. Penggunaan kuasa pula adalah sekitar 0.89mW/saluran dengan gandaan cas sebanyak 3.6mV/fC. Masa puncak denyut yang dihasilkan adalah sekitar 104 ns, ini menunjukkan bahawa ia mampu memproses isyarat kadar tinggi iaitu 333 kHz dengan kurang daripada 5% herotan pada isyarat keluaran. Keputusan ini menunjukkan bahawa reka bentuk litar yang telah direkabentuk dengan menggunakan teknologi 130 nm CMOS dengan transistor masukkan yang beroperasi pada rantau penyongsangan sederhana mempunyai prestasi hingar elektronik yang baik, kadar pembilangan yang tinggi disamping mengurangkan jumlah penggunaan kuasa. Ini juga menunjukkan bahawa litar pembaca bahagian depan ini adalah sesuai untuk digunakan dalam sistem pengesanan zarah neutron.

### ACKNOWLEDGEMENTS

To begin with, all praise and thanks is due to almighty God who gives me the blessing, good health and wisdom to complete my Master research.

First and foremost, I would like to express my deepest appreciation to my supervisor Dr. Roslina Mohd. Sidek, for giving me the opportunity to work under her kind supervision. Her assistance, encouragement, and guidance are endless during my whole Master research work. I am also grateful to my co-supervisors Dr. Mohd. Nizar Hamidon and Dr. Nasri Sulaiman for their invaluable suggestions and guidance during the past two years.

Special thanks also to Dr. Fakhrul Zaman Rokhani for sharing his tremendous and insightful knowledge with me in the area of VLSI design automation. Many thanks also to UPM alumni Lojius bin Lombigit, Master and PhD students in the IC design lab for their suggestions and guidance through my research.

I believe that family deserve the most thanks for the support during my graduate studies. I am especially thankful to my parents who support me mentally and financially, without their patience and support I could not have done my graduate studies. And finally, my wife Salamet, who came into my life during this thesis work, without her love, support, and understanding I could not have succeed.

I certify that a Thesis Examination Committee has met on 29 May 2015 to conduct the final examination of Nueraimaiti Aimaier on his thesis entitled "Design of A Low Noise Low Power Front End Readout Circuit for Neutron Detection Using 130nm CMOS Technology" in accordance with the Universities and University Colleges Act 1971 and the Constitution of the Universiti Putra Malaysia [P.U.(A) 106] 15 March 1998. The Committee recommends that the student be awarded the Master of Science.

Members of the Thesis Examination Committee were as follows:

## Suhaidi bin Shafie, PhD

Associate Professor Faculty of Engineering Universiti Putra Malaysia (Chairman)

**Izhal bin Abdul Halin, PhD** Senior Lecturer Faculty of Engineering Universiti Putra Malaysia (Internal Examiner)

### Nor Hisham Hamid, PhD

Associate Professor Universiti Teknologi Petronas Malaysia (External Examiner)

## **ZULKARNAIN ZAINAL, PhD** Professor and Deputy Dean School of Graduate Studies Universiti Putra Malaysia

Date: 7 June 2015

This thesis was submitted to the Senate of University Putra Malaysia and has been accepted as fulfilment of the requirement for the degree of Master of Science. The members of the Supervisory Committee were as follows:

### Roslina Mohd Sidek, PhD

Associate Professor Faculty of Engineering University Putra Malaysia (Chairman)

### Mohd. Nizar bin Hamidon, PhD

Associate Professor Faculty of Engineering University Putra Malaysia (Members)

# Nasri Sulaiman, PhD

Senior Lecturer Faculty of Engineering University Putra Malaysia (Members)

### **BUJANG BIN KIM HUAT, PhD**

Professor and Dean School of Graduate Studies Universiti Putra Malaysia

Date:

# Declaration by graduate student

I hereby confirm that:

- this thesis is my original work;

- quotations, illustrations and citations have been duly referenced;

- this thesis has not been submitted previously or concurrently for any other degree at any other institutions;

- intellectual property from the thesis and copyright of thesis are fully-owned by Universiti Putra Malaysia, as according to the Universiti Putra Malaysia (Research) Rules 2012;

- written permission must be obtained from supervisor and the office of Deputy Vice-Chancellor (Research and Innovation) before thesis is published (in the form of written, printed or in electronic form) including books, journals, modules, proceedings, popular writings, seminar papers, manuscripts, posters, reports, lecture notes, learning modules or any other materials as stated in the Universiti Putra Malaysia (Research) Rules 2012;

- there is no plagiarism or data falsification/fabrication in the thesis, and scholarly integrity is upheld as according to the Universiti Putra Malaysia (Graduate Studies) Rules 2003 (Revision 2012-2013) and the Universiti Putra Malaysia (Research) Rules 2012. The thesis has undergone plagiarism detection software.

Signature:

Date:

Name and Matric No.: Nueraimaiti Aimaier, GS34530

# **Declaration by Members of Supervisory Committee**

This is to confirm that:

- the research conducted and the writing of this thesis was under our supervision;

- supervision responsibilities as stated in the Universiti Putra Malaysia (Graduate Studies) Rules 2003 (Revision 2012-2013) are adhered to.

| Roslina Mohd |

|--------------|

| Sidek, PhD   |

|              |

Signature: \_\_\_\_\_\_ Name of Member of Supervisory Mohd Nizar Committee: <u>Hamidon, PhD</u>

Signature: \_\_\_\_\_\_ Name of Member of Supervisory Committee: Nasri Sulaiman, PhD

# TABLE OF CONTENTS

|                       | Page |

|-----------------------|------|

| ABSTRACT              | i    |

| ABSTRAK               | iii  |

| ACKNOWLEDGEMENTS      | V    |

| APPROVAL              | vi   |

| DECLARATION           | viii |

| LIST OF TABLES        | xii  |

| LIST OF FIGURES       | xiii |

| LIST OF ABBREVIATIONS | xvii |

|                       |      |

# CHAPTER

| 1 | INTI | RODUCTION                                                           | 1                     |

|---|------|---------------------------------------------------------------------|-----------------------|

|   | 1.1  | Research background                                                 | 1                     |

|   | 1.2  | Neutron detection system                                            | 2                     |

|   | 1.3  | Problem statement and motivation                                    | 2<br>2<br>2<br>3<br>5 |

|   | 1.4  | Research objectives                                                 | 2                     |

|   | 1.5  | Research methodology                                                | 3                     |

|   | 1.6  | Scope of work                                                       | 5                     |

|   | 1.7  | Outline of thesis                                                   | 5                     |

|   |      |                                                                     |                       |

| 2 | LITE | ERATURE REVIEW                                                      | 6                     |

|   | 2.1  | Introduction                                                        | 6                     |

|   | 2.2  | Neutron detectors                                                   | 6                     |

|   | 2.3  | Architecture of readout electronics for neutron detection system    | 8                     |

|   | 2.4  | Signal formation in a detector                                      | 9                     |

|   | 2.5  | Charge sensitive amplifier                                          | 10                    |

|   |      | 2.5.1 Input characteristic of charge sensitive amplifier            | 10                    |

|   |      | 2.5.2 Output characteristics of charge sensitive amplifier          | 11                    |

|   |      | 2.5.3 Preamplifier structure for charge sensitive amplifier         | 12                    |

|   |      | 2.5.4 Reset network implementation for charge sensitive amplifier   | 13                    |

|   | 2.6  | Pulse shaper                                                        | 16                    |

|   |      | 2.6.1 Pole-zero cancellation                                        | 17                    |

|   |      | 2.6.2 Properties and characterization of pulse shaper output signal | 19                    |

|   | 2.7  | Electronic noise                                                    | 20                    |

|   |      | 2.7.1 Noise sources in front-end readout channel                    | 21                    |

|   |      | 2.7.2 Equivalent noise charge (ENC)                                 | 23                    |

|   |      | 2.7.3 Classic ENC optimization methodology                          | 24                    |

|   |      | 2.7.4 ENC optimization for deep-submicron technologies              | 27                    |

|   | 2.8  | Review of related works                                             | 28                    |

|   | 2.9  | Summary                                                             | 30                    |

| • |      |                                                                     | 0.1                   |

| 3 |      | RGE SENSITIVE AMPLIFIER                                             | 31                    |

|   | 3.1  | Noise optimization of charge sensitive amplifier                    | 31                    |

|   |      | 3.1.1 Input transistor selection for CSA                            | 31                    |

|   |      | 3.1.2 Noise optimization using the EKV transistor model             | 33                    |

|   |      | 3.1.3 Secondary noise source optimization                           | 35                    |

|   | 3.2  | Preamplifier design                                                 | 36                    |

|     |      | 3.2.1 Large signal and small signal analysis                       | 37 |

|-----|------|--------------------------------------------------------------------|----|

|     |      | 3.2.2 Transistor sizing for preamplifier                           | 40 |

|     | 3.3  | The CSA reset network and feedback capacitor design                | 44 |

|     | 3.4  | Performance of charge sensitive amplifier                          | 45 |

|     | 3.5  | Summary                                                            | 47 |

| 4   | PUL  | SE SHAPER DESIGN                                                   | 48 |

|     | 4.1  | CR-RC pulse shaper                                                 | 48 |

|     | 4.2  | Pole-zero cancellation circuit design                              | 49 |

|     | 4.3  | Shaper amplifier design                                            | 51 |

|     | 4.4  | CMOS implementation for passive components in the pulse shaper     | 52 |

|     | 4.5  | Summary                                                            | 53 |

| 5   | SIM  | ULATION RESULTS AND DISCUSSION                                     | 54 |

|     | 5.1  | Simulation of complete front-end readout channel                   | 54 |

|     |      | 5.1.1 Power characteristics                                        | 57 |

|     |      | 5.1.2 Transient simulation for charge conversion gain              | 57 |

|     |      | 5.1.3 High counting rate simulation                                | 58 |

|     |      | 5.1.4 Linearity                                                    | 60 |

|     |      | 5.1.5 Noise simulation                                             | 61 |

|     | 5.2  | Layout design                                                      | 63 |

|     |      | 5.2.1 Layout of each component                                     | 65 |

|     |      | 5.2.2 Post-layout simulation                                       | 66 |

|     | 5.3  | Performance of FER circuit and comparison to other published works | 71 |

|     | 5.4  | Summary                                                            | 72 |

| 6   | CON  | ICLUS <mark>ION AND RECOMMENDATION FOR FU</mark> TURE WORKS        | 73 |

|     | 6.1  | Conclusion                                                         | 73 |

|     | 6.2  | Recommendation for future works                                    | 73 |

| REF | EREN | ICES                                                               | 75 |

| APP | ENDI | CES                                                                | 81 |

| BIO | DATA | A OF STUDENT                                                       | 90 |

|     |      |                                                                    |    |

|     |      |                                                                    |    |

|     |      |                                                                    |    |

|     |      |                                                                    |    |

|     |      |                                                                    |    |

|     |      |                                                                    |    |

|     |      |                                                                    |    |

|     |      |                                                                    |    |

# LIST OF TABLES

| Table |                                                                                        | Page |

|-------|----------------------------------------------------------------------------------------|------|

| 1.1   | The design specifications for the front-end readout channel                            | 4    |

| 3.1   | 130nm CMOS technology parameters with their specifications                             | 54   |

| 3.2   | The CSA performances                                                                   | 66   |

| 4.1   | The values of capacitors and resistors in the pulse shaper                             | 70   |

| 5.1   | Power characteristics of complete front-end readout channel                            | 79   |

| 5.2   | The front-end readout system performances and comparison with previous published works | 95   |

C

# LIST OF FIGURES

| Figure |                                                                                                           | Page |

|--------|-----------------------------------------------------------------------------------------------------------|------|

| 1.1    | Helium-3 gas filled proportional counter                                                                  | 2    |

| 1.2    | The research methodology for this work                                                                    | 6    |

| 2.1    | The neutron detection system                                                                              | 9    |

| 2.2    | A neutron interacts with helium nucleus                                                                   | 9    |

| 2.3    | A set of individual gas tubes (left) and multi-wire proportional chamber (right)                          | 10   |

| 2.4    | Two dimensional multi-wire proportional neutron gas                                                       | 11   |

| 2.5    | Neutron detection system including front-end and back-end readout electronics block diagram               | 12   |

| 2.6    | Front-end readout electronics for neutron detector                                                        | 13   |

| 2.7    | Detector signal formation                                                                                 | 14   |

| 2.8    | A current pulse equivalent to 3fC input charge ( <i>Qin</i> )                                             | 14   |

| 2.9    | The miller effect and preamplifier input impedance                                                        | 16   |

| 2.10   | Output of the charge sensitive amplifier                                                                  | 17   |

| 2.11   | Preamplifier structure with PMOS input transistor: (a) folded cascode amplifier, (b) telescopic amplifier | 18   |

| 2.12   | Preamplifier structure with NMOS input transistor: (a) folded cascode amplifier, (b) telescopic amplifier | 19   |

| 2.13   | Reset techniques in charge sensitive amplifier feedback system                                            | 20   |

| 2.14   | Biasing for feedback resistor of charge sensitive amplifier                                               | 22   |

| 2.15   | Pulse pile-up effect at the out of charge sensitive amplifier                                             | 24   |

| 2.16   | Diagram of CR-RC <sup>n</sup> shaping filter                                                              | 24   |

| 2.17   | Voltage pulse at the shaper output for different cases: (a) without PZC circuit, (b) with PZC circuit     | 26   |

| 2.18   | The idea of using PZC circuit after CSA stage                                                             | 26   |

C

| 2.19 | The resistor $(R_{pz})$ implementation in MOS transistor in pole zero cancellation circuit                                                                         | 27 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.20 | MOSFET input-referred channel thermal noise                                                                                                                        | 30 |

| 2.21 | Noise sources in a detector readout system                                                                                                                         | 31 |

| 3.1  | NMOS 1/f and thermal noise voltage spectrum in 130nm CMOS technology                                                                                               | 47 |

| 3.2  | PMOS 1/f and thermal noise voltage spectrum in 130nm CMOS technology                                                                                               | 47 |

| 3.3  | Tansconductance efficiency in different inversion levels                                                                                                           | 50 |

| 3.4  | Targeted values of the detector capacitance $(C_{det})$ , the feedback capacitance $(C_f)$ , the feedback resistance $(R_f)$ , and the shaper peaking time $(T_p)$ | 54 |

| 3.5  | Preamplifier structure with its biasing network                                                                                                                    | 55 |

| 3.6  | Noise performance of CSA versus input transistor transconductance                                                                                                  | 56 |

| 3.7  | PMOS effective voltage versus overdrive voltage in four different channel lengths in 130nm CMOS technology                                                         | 57 |

| 3.8  | Small-signal equivalent circuit of the preamplifier                                                                                                                | 58 |

| 3.9  | The flowchart of design procedures for preamplifier                                                                                                                | 60 |

| 3.10 | Designed geometries of transistors in the preamplifier and the biasing network                                                                                     | 62 |

| 3.11 | Magnitude and phase response of the open loop preamplifier                                                                                                         | 62 |

| 3.12 | The implementation of reset network for CSA                                                                                                                        | 63 |

| 3.13 | The complete designed CSA with its biasing network                                                                                                                 | 65 |

| 3.14 | Response of charge sensitive amplifier to the 10fC input charge                                                                                                    | 66 |

| 4.1  | The first order CR-RC pulse shaper implemented in the front-<br>end readout electronics                                                                            | 69 |

| 4.2  | The pole-zero cancellation circuit implemented in MOS transistors                                                                                                  | 71 |

| 4.3  | Sizing the transistors for pole-zero cancellation circuit                                                                                                          | 72 |

| 4.4  | Shaper amplifier with its biasing network                                                                         | 73 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

| 4.5  | The shaper amplifier magnitude and phase response                                                                 | 73 |

| 4.6  | Shaper resistor $(R_i)$ and capacitor $(C_i)$ implementation in MOS transistors                                   | 74 |

| 5.1  | The front-end readout channel integration                                                                         | 77 |

| 5.2  | Transient response of the complete front-end readout channel                                                      | 78 |

| 5.3  | The floor plan for 32 channels                                                                                    | 78 |

| 5.4  | The current pulse which is equal to 10fC input charge                                                             | 80 |

| 5.5  | The shaper output response to the 10fC input charge                                                               | 80 |

| 5.6  | The shaper output response for input pulse frequency of 100 kHz                                                   | 81 |

| 5.7  | The shaper output response for input pulse frequency of 333 kHz                                                   | 82 |

| 5.8  | The shaper output response for input pulse frequency of 500 kHz                                                   | 82 |

| 5.9  | The shaper output response to different input charges                                                             | 83 |

| 5.10 | Shaper output peak voltage as a function of input charge                                                          | 84 |

| 5.11 | The signal and noise at the output of the complete circuit                                                        | 85 |

| 5.12 | Noise versus detector capacitance                                                                                 | 86 |

| 5.13 | The front-end readout channel that transistors are folded into multi-fingers (n represents the number of fingers) | 87 |

| 5.14 | The complete layout of one channel                                                                                | 88 |

| 5.15 | The layout of preamplifier with its biasing network and feedback capacitor                                        | 88 |

| 5.16 | The layout of adaptive continues reset with charge sensitive amplifier feedback resistor                          | 89 |

| 5.17 | The layout of first order CR-RC pulse shaper                                                                      | 89 |

| 5.18 | Shaper output response to 10fC input charge for post-layout simulation                                            | 90 |

| 5.19 | The shaper output response for input current pulse frequency of 100 kHz after post-layout simulation              | 91 |

- 5.20 The shaper output response for input current pulse frequency of 91 333 kHz after post-layout simulation

- 5.21 The shaper output response for input current pulse frequency of 92 500 kHz after post-layout simulation 92

- 5.22 The shaper output responses to different input charges after post-93 layout simulation

- 5.23 Shaper output peak voltage as a function of input charge after 93 post-layout simulation

- 5.24 The signal at the output of the complete circuit and its 94 corresponding noise after post-layout simulation

95

5.25 Noise versus detector capacitance for post-layout simulation

# LIST OF ABBREVIATIONS

| FER                      | Front-end readout                                    |

|--------------------------|------------------------------------------------------|

| CSA                      | Charge sensitive amplifier                           |

| ADC                      | Analog to digital converter                          |

| CMOS                     | Complementary metal-oxide semiconductor              |

| MOS                      | Metal-oxide semiconductor                            |

| EKV                      | Enz, Krummenacher, Vittoz                            |

| SNR                      | Signal to noise ratio                                |

| DSP                      | Digital signal processing                            |

| DC                       | Direct current                                       |

| NMOS                     | N-type metal-oxide semiconductor                     |

| ASIC                     | Application specific integrated circuit              |

| PMOS                     | P-type metal-oxide semiconductor                     |

| CR-RC <sup>n</sup>       | High pass filter followed by n order low pass filter |

| BPF                      | Band pass filter                                     |

| HPF                      | High pass filter                                     |

| LPF                      | Low pass filter                                      |

| PZC                      | Pole-zero cancellation                               |

| MOSFET                   | Metal-oxide semiconductor field effective transistor |

| Si-SiO <sub>2</sub>      | Silicon and silicon-dioxide                          |

| ENC                      | Equivalent noise charge                              |

| <b>ENC</b> <sub>th</sub> | Equivalent noise charge for thermal noise            |

| $ENC_{1/f}$              | Equivalent noise charge for flicker noise            |

| ENC <sub>d</sub>         | Equivalent noise charge for shot noise               |

| RMS                      | Root mean square                                     |

- GBW Gain bandwidth product

- AC Alternating current

# CHAPTER 1

# INTRODUCTION

## 1.1 Research background

The discovery of neutron particle in 1932 was a significant breakthrough in science history, since then neutron science has been developing rapidly all around the world (Bennington, 2014). One of the most significant applications of neutron science is material testing and investigation. The way neutron scattering off gases, liquids and solid matters give scientists information about the structure and composition of these materials which may be widely used in medicine, mining, transportation, building, engineering, food processing and scientific research. In addition, neutrons serve as the complementary probe to X-rays. While X-rays only penetrate materials near surface, neutrons can penetrate most of the materials to depths of several centimetres, which makes it more effective than X-rays (Schaefer & Agamalian, 2004), (Rubio & Gilbert, 2009), (Oed, 2004).

Generally, neutrons can be detected by using helium-3 (<sup>3</sup>He) filled gas proportional counter. A nuclear reactor ionize the gas inside the detector and generate charged particles. These charged particles are collected by the anode and cathode inside the detector to form a small quantity of current which will be measured by front-end readout circuit as electrical pulses with the amplitude proportional to the neutron energy (Langford, et al., 2013).

## **1.2** Neutron detection system

Since generated electrical signal in the radiation detector is extremely small, in addition to the detector itself does not have its intrinsic amplification stage, a suitable electrical signal processing channel is required to convert this small charges into a voltage pulse large enough to be processed by next subsequent electronic circuits.

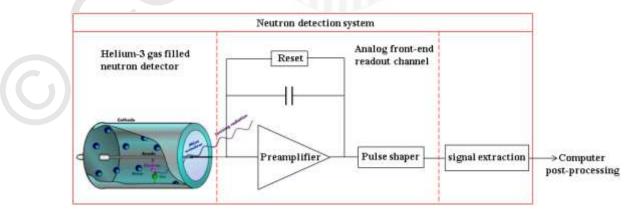

A typical neutron detection system consists of three major blocks: gas filled detector, low noise analog front-end readout (FER) channel, and signal extraction as shown in Figure 1.1. The major function of the detector is to convert the energy released by nuclear reaction to detectable electrical signal.

Figure 1.1. The neutron detection system

The FER channel consisting of a charge sensitive amplifier (CSA) and a pulse shaper which convert input charges into voltage pulse then produce a Gaussian-like pulse that carries the information of energy spectroscopy and timing. The signal extraction block may consists of mixed mode circuits such as analog-to-digital converter (ADC), comparator or discriminator, etc. to process the Gaussian-like pulse for peak amplitude and time measurements, and counting rate which is manipulated by computer post-processing (Spieler, 2005).

## **1.3** Problem statement and motivation

To detect the neutron which is captured in <sup>3</sup>He gas filled detector, specific readout electronics is needed. Existing FER electronics are mostly implemented using off-the-shelf op amps (operational amplifiers) and discrete passive components suffers from high power consumption and occupy large area which limits the number of readout channels.

Analog FER electronics based on CMOS technology has power efficiency, occupy only micrometres square area, and is inexpensive. CMOS technology has been adopted to FER circuit since decades though, most of them still limited by noise performance and power consumption. As CMOS technology experiences continues down scaling, accurate MOS transistor modelling is required. This puts challenges to front-end designers to use low power while achieving high signal-to-noise ratio (SNR). Low FER channel power consumption in the range of a few mW is required to minimize the total detector system power consumption.

An efficient CMOS analog circuit design methodology which is using EKV model based on a unified treatment of all the regions of operation of the MOS transistor can be quite successful in terms of low power circuit design where the moderate inversion region is often used because it provides a good trade-off between speed and power consumption. In order to achieve better signal resolution, the signal-to-noise ratio above 125:1 is recommended. Since the time between nuclear radiation events is short, in high counting rate applications, it requires a short peaking time for pulse shaper in the range of a few hundred nanoseconds. Compare to some recent published works (Lombigit, Hamidon, Khalid, & Sulaiman, 2012), (Fang, Hu-Guo, Brasse, & Hu, 2011) and (Noulis, Siskos, Sarrabayrouse, & Bary, 2008) some better design specifications are targeted in this work which are given in Table 1.1.

| Signal-to-noise ratio | Power per channel | Shaper peaking time |

|-----------------------|-------------------|---------------------|

| 125:1                 | <1 mW             | 100 ns              |

# **1.4 Research objectives**

The aim of the research is to design low power consumption and low noise CMOS readout circuits for neutron detectors. The main objectives of this research are:

- To investigate and develop methodologies for optimizing noise in CMOS analog FER circuit

- To design a low noise, low power analog FER circuit with short peaking time using commercial 130nm CMOS technology

• To evaluate the characteristics and performance of the circuit in terms of output gain, electronic noise and dynamic range

The expected major contribution of this thesis is development of a methodology to investigate and optimize noise sources of analog FER circuit to achieve low noise performance while keeping the power consumption as small as possible in deep submicron CMOS technology.

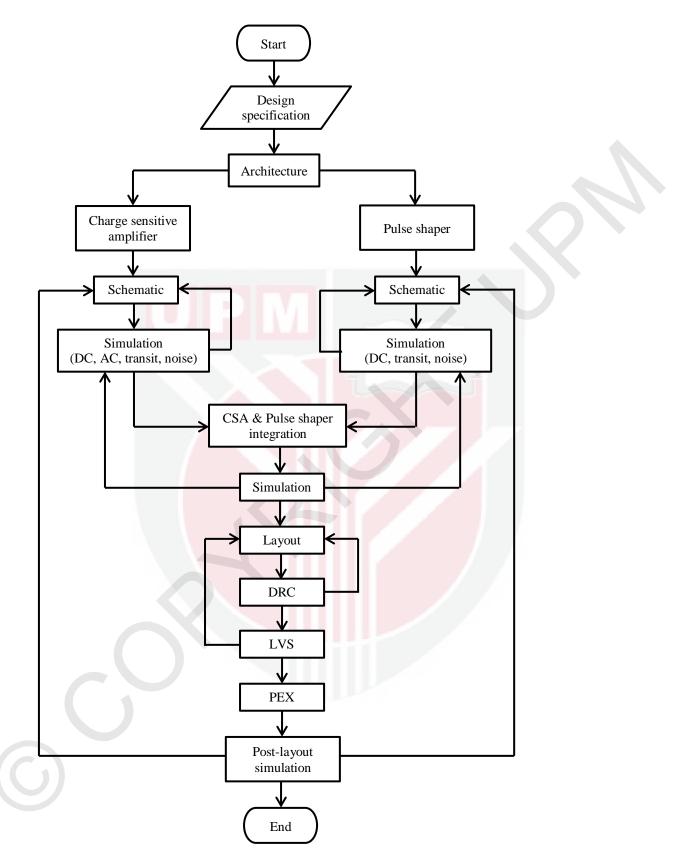

## 1.5 Research methodology

The research methodology for this work is shown in Figure 1.2. From design specifications the architectures of the FER circuit which consists of charge sensitive amplifier and pulse shaper have been designed. Then schematic captures and simulation (DC, AC, transit, noise) for each block (charge sensitive amplifier and pulse shaper) have been done. After passing the simulations results of each block, the CSA and pulse shaper are integrated to form a FER circuit and a variety of simulations are done to validate the performances of circuit, and redesign has been done if targeted performances are not achieved. The layout of the circuit has been done in IC station and validations of the layout have been done such as design rules check (DRC) and layout versus schematic (LVS). After passing these validation processes, parasitic extraction (PEX) and post-layout simulations have been conducted to ensure the pre-targeted specifications for the FER system are achieved.

Figure 1.2. The research methodology for this work

# **1.6** Scope of work

This thesis presents a readout integrated circuit for neutron detector system based on 130nm CMOS technology. The focus of this work is noise optimization for FER circuit. The key tasks are design of low power, low noise, and short peaking time analog FER circuit which consists of charge sensitive amplifier and pulse shaper, evaluate performance of the circuit, and finally design of the CMOS integrated circuit layout.

# 1.7 Outline of thesis

The thesis is structured in six chapters. Chapter 1 is introduction to research background. Chapter 2 presents a review of literatures of neutron detectors, analog FER electronics and its each component. The detailed design procedure of the charge sensitive amplifier is presented in Chapter 3. Chapter 4 covers design of the pulse shaper. The simulation results, layout design and discussions are presented in Chapter 5. Chapter 6 covers the conclusion of the work and future recommendation.

#### REFERENCES

- Allen, P. E., Holberg, D. R. (2002). *CMOS analog circuit design.* (2nd ed.). New York: Oxford University Press.

- Amin, F. U., Svensson, C., & Gustavsson, M. (2010). Low-power, high-speed, and low-noise X-ray readout channel in 0.18µm CMOS. Proceedings of the 17th International Conference on Mixed Design of Integrated Circuits and Systems (MIXDES) (pp. 289-293). Warsaw: IEEE.

- Baker, J. R. (2010). *CMOS circuit design, layout, and simulation* (3rd ed.). New Jersey: John Wiley & Sons.

- Baschirotto, A., Cocciolo, G., Matteis, M. D., Giachero, A., Gotti, C., Maino, M., et al. (2012). A fast and low noise charge sensitive preamplifier in 90 nm CMOS technology. *Journal of Instrumentation*, 7(1), 1-8.

- Belushkin, A. V. (2008). Modern trends in the development of position sensitive neutron detectors for condensed matter research. *Pramana*, 71(4), 639-651.

- Bennington, S. M. (2014, January 1). ISIS Neutron Training Course. Retrieved December 26, 2014, from Science & Technology Facilities Council: http://www.isis.stfc.ac.uk/learning/neutron-trainingcourse/downloads/general/neutron-training-course---manual13577.pdf

- Britton, J. L., Bunch, S. C., Britton, C. L., Blalock, B. J., McGregor, D. S., & Crow, L. (2006). PATARA: solid-state neutron detector readout electronics with pole-zero and complex shaping and gated baseline restorer for the SNS. *IEEE Conference Record of Nuclear Science Symposium*, 27-31.

- Carusone, T. C., Johns, D. A., & Martin, K. W. (2012). Analog integrated circuit design. New Jersey: Wiley.

- Chang, Z. Y., & Sansen, W. M. (1991). Low-noise wide-band amplifiers in bipolar and CMOS technologies. New York: Kluwer Academic Publishers.

- Characteristics and use of charge amplifier. (2001). Retrieved from HAMAMATSU Solid State Division: Technical Information SD-37: http://www.hamamatsu.com/resources/pdf/ssd/charge\_amp\_techinfo\_e.pdf

- De Geronimo, G., & O'Conner, P. (1999). A CMOS detector leakage current selfadaptable continuous reset system: Theoretical analysis. *Nuclear Instruments* and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 421(1-2), 322-333.

- De Geronimo, G., & O'Conner, P. (2000). A CMOS fully compensated continuous reset system. *IEEE Transactions on Nuclear Science*, 47(4), 1458-1462.

- De Geronimo, G., & O'Conner, P. (2005). MOSFET optimization in deep submicron technology for charge amplifiers. *IEEE Transactions on Nuclear Science*, 52(6), 3223-3232.

- Enz, C. C., Krummenacher, F., & Vittoz, E. A. (1995). An Analytical MOS Transistor Model Valid in All Regions of Operation and Dedicated to Low-Voltage and Low-Current Applications. *Analog Integrated Circuits and Signal Processing*, 8, 83-114.

- Fang, X. C., Hu-Guo, C., Brasse, D., & Hu, Y. (2011). Design and characterization of a multi-channel front-end readout ASIC with low noise and large dynamic input range for APD-based PET imaging. *Analog Integrated Circuits and Signal Processing*, 66(1), 31-40.

- Geronimo, G. D., O'Conner, P., Radeka, V., & Yu, B. (2001). Front-end electronics for imaging detectors. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 471(1-2), 192-199.

- Gramegna, G., O'Conner, P., Rehak, P., & Hart, S. (1997). CMOS preamplifier for low-capacitance detectors. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 390(1-2), 241-250.

- Gramegna, G., O'Connor, P., Rehak, P., & Hart, S. (1997). Low-noise CMOS preamplifier-shaper for silicon drift detectors. *IEEE Transactions on Nuclear Science*, 44(3), 385-388.

- Grybos, P. (2010). Front-end Electronics for Multichannel Semiconductor Detector Systems. Warsaw: European Coordination for Accelerator Research and Development.

- Grybos, P., Idzik, M., & Maj, P. (2007). Noise Optimization of Charge Amplifiers With MOS Input Transistors Operating in Moderate Inversion Region for Short Peaking Times. *IEEE Transactions on Nuclear Science*, 54(3), 555-560.

- Grybos, P., Idzik, M., Swientek, K., & Maj, P. (2006). Integrated charge sensitive amplifier with pole-zero cancellation circuit for high rates. *IEEE International Symposium on Circuits and Systems, 2006. ISCAS 2006. Proceedings* (pp. 1997-2000). Island of Kos: IEEE.

- Grybos, P., Izdik, M., & Skoczen, A. (2006). Design of low noise charge amplifier in sub-micron technology for fast shaping time. *Analog Integrated Circuits and Signal Processing*, 49(2), 107-114.

- Grybos, P., Maj, P., & Szczygiel, R. (2007). Comparison of Two Pole-Zero Cancellation Circuits for Fast Charge Sensitive Amplifier in CMOS Technology. 14th International Conference on Mixed Design of Integrated Circuits and Systems (pp. 243-246). Ciechocinek: IEEE.

- Hu, Y., Berst, J. D., & Schaeffer, M. (1998). A Very Low Power Consumption, Low Noise Analog Readout Chip for Capacitive Detectors with a Power Supply of 3.3 V. Analog Integrated Circuits and Signal Processing, 17(3), 249-260.

- Hu, Y., Solere, J. L., Lachartre, D., & Turchetta, R. (1998). Design and performance of a low-noise, low-power consumption CMOS charge amplifier for capacitive detectors. *IEEE Transactions on Nuclear Science*, 45(1), 119-123.

- Kleczek, R., Otfinowski, P., & Grybos, P. (2012). Area efficient front-end readout electronics for pixel detector based on inverter amplifier. *Mixed Design of Integrated Circuits and Systems* (pp. 219-222). Warsaw: IEEE.

- Lam, S. (2012, March 19). Helium-3 Proportional Counters and Alternatives for Neutron Detection. Retrieved December 26, 2014, from Introduction to Nuclear Energy: http://large.stanford.edu/courses/2012/ph241/lam1/

- Langford, T. J., Bass, C. D., Beise, E. J., Breuer, H., Erwin, D. K., Heimbach, C. R., et al. (2013). Event identification in 3He proportional counters using risetime discrimination. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 717, 51-57.

- Lombigit, L., Hamidon, M. N., Khalid, M. A., & Sulaiman, N. (2012). Low cost front-end readout electronic for instrumentation used in neutron experiments. *International Journal of Physical Sciences*, 7(20), 2812-2817.

- Manghisoni, M., Ratti, L., Re, V., & Speziali, V. (2002). Low-noise design criteria for detector readout systems in deep submicron CMOS technology. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 478(1-2), 362-366.

- Manghisoni, M., Ratti, L., Re, V., & Speziali, V. (2002). Submicron CMOS technologies for low-noise analog front-end circuits. *IEEE Transactions on Nuclear Science*, 49(4), 1783-1790.

- Manghisoni, M., Ratti, L., Re, V., Speziali, V., & Traversi, G. (2006). Noise Performance of 0.13um CMOS Technologies for Detector Front-End Applications. *IEEE Transactions on Nuclear Science*, 53(4), 2456-2462.

- Manghisoni, M., Ratti, L., Re, V., Speziali, V., & Traversi, G. (2007). Resolution Limits in 130 nm and 90 nm CMOS Technologies for Analog Front-End Applications. *IEEE Transactions on Nuclear Science*, 54(3), 531-537.

- Manghisoni, M., Ratti, L., Re, V., Speziali, V., & Traversi, G. (2007). Resolution Limits in 130 nm and 90 nm CMOS Technologies for Analog Front-End Applications. *IEEE Transactions on Nuclear Science*, 54(3), 531-537.

- Mazed, D., Mameri, S., & Ciolini, R. (2012). Design parameters and technology optimization of 3He-filled proportional counters for thermal neutron

detection and spectrometry applications. *Radiation Measurements*, 47(8), 577-587.

- Ming-Cheng, L., & Syrzycki, M. (2011). Current source transistor optimization methodology for noise optimized charge sensitive amplifier with fast shaper. 24th Canadian Conference on Electrical and Computer Engineering (CCECE) (pp. 735-738). Niagara Falls, ON: IEEE.

- Ming-Cheng, Lin (2012). Low Noise Analog Front-End Signal Processing Channel Integration for Pixelated Semiconductor Radiation Detector. *Master Thesis, Simon Fraser University, Canada.*

- Moser, H. G. (2009). Silicon detector systems in high energy physics. *Progress in Particle and Nuclear Physics*, 63(1), 186-237.

- Noulis, T., Deradonis, C., Siskos, S., & Sarrabayrouse, G. (2007). Detailed study of particle detectors OTA-based CMOS Semi-Gaussian shapers. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 583(2-3), 469-478.

- Noulis, T., Siskos, S., & Sarrabayrouse, G. (2004). Effect of Technology on the Input Transistor Selection Criteria of a Low Noise Preamplifier. *Proceedings of the 12th IEEE Mediterranean Electrotechnical Conference, 2004. MELECON. 1*, pp. 51-54. Dubrovnik: IEEE.

- Noulis, T., Siskos, S., Sarrabayrouse, G., & Bary, L. (2008). Advanced Low-Noise X-Ray Readout ASIC for Radiation Sensor Interfaces. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 55(7), 1854-1862.

- O'Conner, P., & Geronimo, G. D. (2002). Prospects for charge sensitive amplifiers in scaled CMOS. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 480(2-3), 713-725.

- Oed, A. (2004). Detectors for thermal neutrons. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 525(1-2), 62-68.

- Osberg, K., Schemm, N., Balkir, S., Brand, J. I., Hallbeck, M. S., Dowben, P. A., et al. (2006). A Handheld Neutron-Detection Sensor System Utilizing a New Class of Boron Carbide Diode. *IEEE Sensors Journal*, 6(6), 1531-1538.

- Patriot, P. (2011, November 15). DNDO Identifies Helium-3 Replacements for Neutron Detection. Retrieved Febuary 10, 2015, from Tea Party Tribune: http://www.teapartytribune.com/2011/11/15/dndo-identifies-helium-3replacements-for-neutron-detection/

- Pratte, J. F., Robert, S., De Geronimo, G., O'Conner, P., Stoll, S., Pepin, C. M., et al. (2004). Design and performance of 0.18-µm CMOS charge preamplifiers for

APD-based PET scanners. *IEEE Transactions on Nuclear Science*, 51(5), 1979-1985.

- Pratte, J. F., Robert, S., Geronimo, G. D., O'Conner, P., Stoll, S., Pepin, C. M., et al. (2004). Design and performance of 0.18-µm CMOS charge preamplifiers for APD-based PET scanners. *IEEE Transactions on Nuclear Science*, 51(5), 1979-1985.

- Radeka, V. (2012, August 1). *Gas-based Thermal Neutron Detectors*. New York: Brookhaven National Laboratory.

- Razavi, B. (2001). Design of analog CMOS integrated circuits. McGraw-Hill.

- Re, V., Manghisoni, M., Ratti, L., Speziali, V., & Traversi, G. (2006). Design criteria for low noise front-end electronics in the 0.13 μm CMOS generation. Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 568(1), 343-349.

- Rubio, A. L., & Gilbert, E. P. (2009). Neutron scattering: a natural tool for food science and technology research. *Trends in Food Science & Technology*, 20(11-12), 576-586.

- Sansen, W., & Zhong, Y. C. (1990, November). Limits of low noise performance of detector readout front ends in CMOS technology. *IEEE Transactions on Circuits and Systems*, 37(11), 1375-1382.

- Schaefer, D. W., & Agamalian, M. M. (2004). Ultra-small-angle neutron scattering: a new tool for materials research. *Current Opinion in Solid State and Materials Science*, 8(1), 39-47.

- Schemm, N., Balkir, S., Hoffman, M. W., Bauer, M., Schultz, D., Petrosky, J. C., et al. (2010). A Single Chip Computational Sensor System for Neutron Detection Applications. *IEEE Sensors Journal*, 10(7), 1226-1233.

- Spieler, H. (2005). *Semiconductor Detector Systems*. New York: Oxford University Press.

- Sundstrom, T., Murmann, B., & Svensson, C. (2009). Power Dissipation Bounds for High-Speed Nyquist Analog-to-Digital Converters. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 56(3), 509-518.

- Szczygiel, R., Grybos, P., & Maj, P. (2008). Noise optimization of fast charge sensitive amplifier in submicron technology for low power application. 15th International Conference on Mixed Design of Integrated Circuits and Systems, 2008. MIXDES (pp. 81-84). Poznan: IET.

- Tsoulfanidis, N. (1995). *Measurement and detection of radiation*. Washington, D.C.: Taylor & Francis.

- Weste, N. H., Harris, D. M. (2011). CMOS VLSI design: a circuits and systems perspective. (4th ed.). Addison-Wesley.

- Zhang, Y., Husson, D., Le, T. D., Higueret, S., Hu-Guo, C., & Hu, Y. (2011). Development of an integrated CMOS sensor for efficient neutron counting. *Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC)* (pp. 409-415). Valencia: IEEE.