# **UNIVERSITI PUTRA MALAYSIA**

# PROCESS CONSOLIDATION OF BORON STEAM AND EMITTER DIFFUSION IN PNP BIPOLAR TRANSISTOR FABRICATION

# KADER IBRAHIM ABD WAHAB

FK 2003 22

## PROCESS CONSOLIDATION OF BORON STEAM AND EMITTER DIFFUSION IN PNP BIPOLAR TRANSISTOR FABRICATION

By

KADER IBRAHIM ABD WAHAB

,

Thesis Submitted to the School of Graduate Studies, Universiti Putra Malaysia, in Partial Fulfillment of the Requirements for the Degree of Master of Science

March 2003

$\mathbf{x}$

## **DEDICATION**

To my children, Syazwani, Safiah and Sarah, You are my pride and inspiration.

*To my wife and life partner*, thank you for your continuous support, patience, encouragement and motivation.

Abstract of thesis submitted to the Senate of Universiti Putra Malaysia in partial fulfillment of the requirements for the degree of Master of Science

## PROCESS CONSOLIDATION OF BORON STEAM AND EMITTER DIFFUSION IN PNP BIPOLAR TRANSISTOR FABRICATION

By

## KADER IBRAHIM ABD. WAHAB

### March 2003

#### Chairman: Associate Professor Shamsuddin Sulaiman, Ph.D.

#### Faculty: Engineering

Boron Steam is a process done after boron emitter diffusion for all PNP transistors and diodes. Boron emitter diffusion is a process to dope the emitter well with P-type dopant. The source of this dopant is in the form of liquid spun on the wafers and exposed to high temperatures. Boron steam is done to basically soften the residual liquid boron prior to cleaning for easy removal. This project will cover hardware comparison and recipe proposal that were used. The new consolidated process has resulted in comparable final in-line measurement of oxide thickness and test results. Reliability expectation was also met with 1000 cycles of Intermittent Operating Life test. Significant cost advantages were also achieved.

Abstrak untuk tesis ini dikemukakan kepada Senat Universiti Putra Malaysia sebagai memenuhi sebahagian dari keperluan untuk ijazah Master Sains

## PENGGABUNGAN PROSES PENGWAPAN BORON DAN RESAPAN PEMANCAR DIDALAM PEMBIKINAN TRANSISTOR DWIPOLAR JENIS PNP

Oleh

#### KADER IBRAHIM ABD. WAHAB

### **Mac 2003**

### Pengerusi: Profesor Madya Shamsuddin Sulaiman, Ph.D.

#### Fakulti: Kejuruteraan

Pengwapan boron adalah salah satu dari proses yang dilakukan selepas proses resapan pemancar keatas semua transistor jenis PNP dan diod. Resapan pemancar dengan bendasing boron adalah proses di mana kawasan pemancar diperkayakan dengan bendasing jenis-P. Sumber bendasing jenis-P ini adalah dalam bentuk cecair yang disembur ke atas wafer untuk membentuk lapisan yang rata dan wafer itu kemudian didedahkan pada suhu yang tinggi. Pengwapan boron dilakukan untuk melembutkan lapisan baki boron yang berlebihan yang tidak digunakan. Ini adalah untuk memudahkan pembersihan lapisan baki di atas wafer. Projek ini akan meliputi perbandingan perkakasan yang digunakan dan cadangan resepi yang digabungkan. Proses baru yang telah digabungkan dapat memenuhi kesemua kehendak kritikal dalam pemprosesan dan juga ujian elektrik terakhir. Ujian keboleharapan yang dilakukan juga menunjukkan tiada sebarang masalah dengan proses baru. Terdapat juga penjimatan kos setelah melaksanakan projek ini.

### ACKNOWLEDGEMENTS

I would like to thank the chairman of the supervisory committee, Associate Professor Dr. Shamsuddin Sulaiman for his patience, support, supervision and guidance. Many thanks to Dr. Roslina Mohd Sidek and Associate Professor Dr. A.M.S. Hamouda as the committee member for this project for sharing their knowledge and for their constructive criticisms and suggestions.

My sincere appreciation to the chairman of the examination committee, Associate Professor Dr. Megat Mohamad Hamdan Megat Ahmad for his suggestions, recommendations, criticisms and support.

My sincere gratitude is extended to all staff of Motorola ISMF wafer fabrication facility in Seremban for their support and help in realizing this project.

I would like to acknowledge SC Low for giving me the opportunity and guidance while executing this project.

## **TABLE OF CONTENTS**

| ii   |

|------|

| iii  |

| iv   |

| v    |

| vi   |

| vii  |

| viii |

| xi   |

| xii  |

| xv   |

|      |

## CHAPTER

| 1 | INTR | INTRODUCTION                                    |    |

|---|------|-------------------------------------------------|----|

|   | 1.1  | Bipolar Integrated Circuit Process Flow         | 2  |

|   | 1.2  | Uses of Bipolar Transistors                     | 4  |

|   | 1.3  | Statement of Problem                            | 5  |

|   | 1.4  | Objective of Project                            | 6  |

|   | 1.5  | Scope and Limitation                            | 6  |

|   | 1.6  | Expected Outcome                                | 6  |

| 2 | LITE | RATURE REVIEW                                   | 7  |

|   | 2.1  | Introduction                                    | 7  |

|   | 2.2  | Bipolar Junction Transistor Operations          | 8  |

|   | 2.3  | Bipolar Wafer Fabrication                       | 10 |

|   | 2.4  | The Diffusion Process                           | 22 |

|   |      | 2.4.1 Diffusion Process Equipment               | 24 |

|   |      | 2.4.2 The Thermal Oxidation of Silicon          | 26 |

|   | 2.5  | Available Method of Forming Emitter Junction in |    |

|   |      | a PNP transistor                                | 27 |

|   |      | 2.5.1 Ion Implantation                          | 27 |

|   |      | 2.5.2 Solid Source Diffusion                    | 27 |

|   |      | 2.5.3 Doping Diffusion                          | 28 |

|   |      | 2.5.4 Spin-On Dopant                            | 28 |

|   | 2.6  | Available Source of Boron Dopants               | 28 |

|   | 2.7  | Detail Fabrication Process of Emitter Junction  |    |

|   |      | Formation                                       | 29 |

|   | 2.8  | Problems Associated with Spin-On Method         | 32 |

| 3   | MET    | HODOLOGY                               | 34 |

|-----|--------|----------------------------------------|----|

|     | 3.1    | Introduction                           | 34 |

|     | 3.2    | Overview of the project                | 35 |

|     | 3.3    | Process Development                    | 35 |

|     | 3.4    | Process Changes                        | 36 |

|     | 3.5    | Process Comparison                     | 36 |

|     | 3.6    | External Torch                         | 37 |

|     | 3.7    | Process Recipe Comparison              | 38 |

| 4   | EXP    | ERIMENTAL                              | 40 |

|     | 4.1    | Introduction                           | 40 |

|     | 4.2    | Steam Time evaluation                  | 40 |

|     | 4.3    | Final Consolidated Recipe              | 42 |

|     | 4.4    | Measurement Tools and Method           | 45 |

| 5   | RES    | ULTS AND DISCUSSION                    | 46 |

|     | 5.1    | Steam Time Evaluation                  | 46 |

|     | 5.2    | Electrical Results                     | 47 |

|     | 5.3    | Oxide Thickness Comparison After Steam | 50 |

|     | 5.4    | Oxide Etch Rate After Steam            | 51 |

|     | 5.5    | Visual Appearance After Steam          | 51 |

|     | 5.6    | Reliability Results                    | 52 |

|     | 5.7    | Cost Reductions                        | 54 |

|     | 5.8    | Other Advantages                       | 54 |

| 6   | CON    | ICLUSION AND RECOMMENDATION            | 55 |

| REF | FERENC | CES                                    | 57 |

# LIST OF TABLES

| Table |                                                   | Page |

|-------|---------------------------------------------------|------|

| 2.1   | Different type of boron dopants available         | 28   |

| 3.1   | Comparison between the 2 furnaces                 | 36   |

| 4.1   | Lot and device type selection for experimentation | 44   |

| 5.1   | Results of lot 1, 2 and 3                         | 49   |

| 5.2   | Results for lot 4                                 | 50   |

| 5.3   | Cost Savings                                      | 54   |

## LIST OF FIGURES

| Figure |                                                                      | Page |

|--------|----------------------------------------------------------------------|------|

| 1.1    | pnp transistor                                                       | 2    |

| 1.2    | npn transistor                                                       | 2    |

| 1.3    | Simplified Bipolar process flow chart                                | 3    |

| 1.4    | Bipolar device cross section                                         | 4    |

| 2.1    | Two brick diodes forming a bipolar transistor                        | 8    |

| 2.2    | Wafer after initial oxidation                                        | 10   |

| 2.3    | Wafer after base photo patterning                                    | 11   |

| 2.4    | Wafer after base etching                                             | 11   |

| 2.5    | Wafer after base photoresist removal                                 | 11   |

| 2.6    | After pre-implant oxide growth                                       | 12   |

| 2.7    | Ion being implanted                                                  | 12   |

| 2.8    | After implantation a layer of oxide deposited on wafer               | 13   |

| 2.9    | Showing base drive-in forming and activating the implanted base area | 13   |

| 2.10   | Emitter photo patterning done                                        | 14   |

| 2.11   | After emitter etching                                                | 14   |

| 2.12   | After boron coating on wafer surface                                 | 15   |

| 2.13   | Remaining residual boron after emitter diffusion                     | 15   |

| 2.14   | Residual boron ready for removal                                     | 16   |

| 2.15 | Base and emitter junction formed                                                                                                                                                                                                                                                                                                          | 16 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.16 | A layer of oxide deposited for N+ photoresist process                                                                                                                                                                                                                                                                                     | 17 |

| 2.17 | N+ pattern transferred and etched to open the area                                                                                                                                                                                                                                                                                        | 17 |

| 2.18 | N+ diffusion done to dope the area with high concentration of N-type material                                                                                                                                                                                                                                                             | 18 |

| 2.19 | Contact area patterned and etched                                                                                                                                                                                                                                                                                                         | 18 |

| 2.20 | A layer of metal film (Al-Si) deposited                                                                                                                                                                                                                                                                                                   | 19 |

| 2.21 | Metal photo and etch done to remove unwanted metal                                                                                                                                                                                                                                                                                        | 19 |

| 2.22 | A layer of passivation (Silicon Nitride) deposited                                                                                                                                                                                                                                                                                        | 20 |

| 2.23 | Passivation photo and etch done to expose the bonding pads                                                                                                                                                                                                                                                                                | 20 |

| 2.24 | A layer of gold evaporated to the wafer backside                                                                                                                                                                                                                                                                                          | 21 |

| 2.25 | Horizontal Diffusion Furnace Layout. This is a cutaway view of the horizontal diffusion furnace. The gas-<br>control and temperature-control systems are shown, along with the wafer loader system, shown in the standby " <i>out</i> " position and in the active " <i>in</i> " position. Hot exhaust gases are trapped and vented away. | 25 |

| 2.26 | Cross section prior to boron emitter diffusion                                                                                                                                                                                                                                                                                            | 29 |

| 2.27 | Wafer coated with boron dopant ready for drive in                                                                                                                                                                                                                                                                                         | 30 |

| 2.28 | Wafer coated with boron dopant ready for drive in                                                                                                                                                                                                                                                                                         | 30 |

| 2.29 | Emitter junction formed with residual boron still on top of wafer surface and hardened                                                                                                                                                                                                                                                    | 31 |

| 2.30 | Wafer has been subjected to boron steam and the residual boron is now soaked and is much easier to clean                                                                                                                                                                                                                                  | 31 |

| 2.31 | Final cross section after boron steam and cleaning                                                                                                                                                                                                                                                                                        | 32 |

| 3.1  | Process Flow of Project                                                                                                                                                                                                                                                                                                                   | 35 |

| 3.2 | Current boron emitter diffusion recipe | 38 |

|-----|----------------------------------------|----|

| 3.3 | Current Boron Steam Recipe             | 39 |

| 4.1 | Experimental Groups                    | 41 |

| 4.2 | Final Consolidated recipe              | 43 |

| 5.1 | Results after evaluation               | 47 |

| 5.2 | Reliability Report Summary Part 1      | 52 |

| 5.3 | Reliability Report Summary Part 2      | 53 |

## LIST OF ABBREVIATIONS

| P-type                                   | majority carriers of charge are holes                                                                                                                                                                              |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N-type                                   | majority carriers of charge are electrons                                                                                                                                                                          |

| PNP                                      | Transistor (emitter is P-type, base is N-type, collector is P-type)                                                                                                                                                |

| NPN                                      | Transistor (emitter is N-type, base is P-type, collector is N-type)                                                                                                                                                |

| TEOS                                     | Tetra Ethyl Ortho Silicate                                                                                                                                                                                         |

| PH <sub>3</sub>                          | Phosphine                                                                                                                                                                                                          |

| SiO <sub>2</sub>                         | Silicon Dioxide                                                                                                                                                                                                    |

| Si <sub>3</sub> N <sub>4</sub>           | Silicon Nitride                                                                                                                                                                                                    |

| PECVD                                    | Plasma enhanced chemical vapour deposition                                                                                                                                                                         |

|                                          |                                                                                                                                                                                                                    |

| LPCVD .                                  | Low Pressure chemical vapour deposition                                                                                                                                                                            |

| LPCVD<br>CpK                             | Low Pressure chemical vapour deposition<br>Process capability index                                                                                                                                                |

|                                          |                                                                                                                                                                                                                    |

| СрК                                      | Process capability index                                                                                                                                                                                           |

| CpK<br>Å                                 | Process capability index<br>Angstrom (1 x 10 <sup>-10</sup> m)                                                                                                                                                     |

| ČpK<br>Å<br>САВ                          | Process capability index<br>Angstrom (1 x 10 <sup>-10</sup> m)<br>change action board                                                                                                                              |

| Å<br>CAB<br>IOL                          | Process capability index<br>Angstrom (1 x 10 <sup>-10</sup> m)<br>change action board<br>Intermittent Operating Life                                                                                               |

| ČpK<br>Å<br>CAB<br>IOL<br>CMOS           | Process capability index<br>Angstrom (1 x 10 <sup>-10</sup> m)<br>change action board<br>Intermittent Operating Life<br>Complimentary metal oxide semiconductor                                                    |

| ĈpK<br>Å<br>CAB<br>IOL<br>CMOS<br>BiCMOS | Process capability index<br>Angstrom (1 x 10 <sup>-10</sup> m)<br>change action board<br>Intermittent Operating Life<br>Complimentary metal oxide semiconductor<br>Bipolar complimentary metal oxide semiconductor |

| $B_2O_5$ | Boron Pentoxide                            |

|----------|--------------------------------------------|

| B-75     | Liquid boron in Toluene (Brand name)       |

| UV       | Ultra violet                               |

| DCE      | Dichloro ethylene                          |

| HF       | Hydrofluoric Acid                          |

| Al-Si    | Aluminum Silicon                           |

| Hfe      | transistor gain (direct current)           |

| Vbef     | Voltage drop between base and emitter      |

| Vbcf     | Voltage drop between base and collector    |

| Vce      | Voltage drop between collector and emitter |

| Icbo     | Collector-base leakage                     |

| Icev     | Collector-emitter leakage                  |

| BJT      | Bipolar Junction Transistor                |

### **CHAPTER 1**

#### **INTRODUCTION**

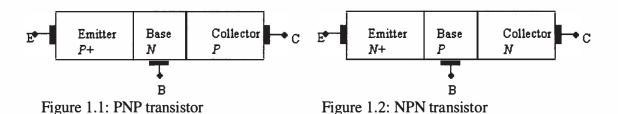

This project is related to the fabrication of bipolar transistors and diodes. The bipolar transistor is a two-junction, three layer device in which the current can flow. One p-n junction can be modulated by interaction with another nearby p-n junction. The structure maybe either p-n-p or n-p-n, but only P-N-P devices will be discussed, since the N-P-N transistor does not go through the boron emitter diffusion nor the boron steam processing. However the results are applicable to N-P-N transistors with appropriate change of polarities. Figure 1.1 and 1.2 shows the PNP and the NPN bipolar transistor respectively. Bipolar transistors were the first type of solid state amplifying devices commercially available. The electrical characteristics of a bipolar transistor are determined primarily by the bulk properties of the semiconductor material used for its manufacture. The discrete devices and integrated circuits produced by the semiconductor industry up through the late 1960s were largely fabricated using bipolar technology. Due to their early technology lead and their intrinsic characteristics, bipolar devices continue to be used advantageously both as discrete components and as devices in integrated circuits. Today, bipolar integrated circuits and bipolar devices combined with CMOS devices in BiCMOS integrated circuits are significant factors in the marketplace.

The essential features of the bipolar transistors are:-

- Two junction diodes that share a common base region. This can form an n+pn or p+np bipolar transistor.

- > The emitter material is heavily doped compared to the base material.

- The lifetime of the minority carrier in the base is sufficient that these carriers can drift and diffuse to the base collector depletion region, where they are collected. The base width is the critical dimension in the transistor.

- The doping profiles in the base and collector must form a reverse biased diode with sufficient reverse breakdown voltage for the application.

### 1.1 Bipolar Integrated Circuit Process Flow

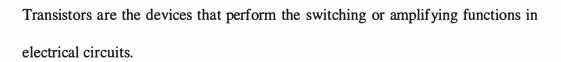

The fabrication processes for bipolar transistors, particularly as an element in an IC, are extremely varied. All processes, however, contain these basic elements:

- Formation of collector material

- Formation of the device isolation

- Formation of the base and emitter regions

An IC process for a traditional bipolar structure is shown in Figure 1.3

Figure 1.3. Simplified Bipolar Process Flow Chart[4].

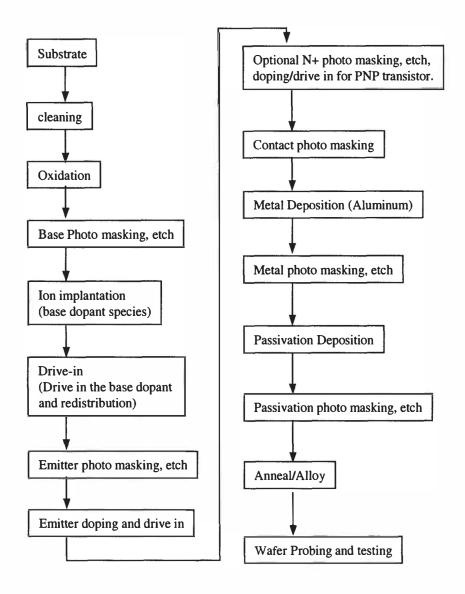

The isolated regions formed within the n-epi tubs are used for the fabrication of the NPN bipolar transistors. The device cross section is shown in Figure 1.4, where the material marked by the small box is the active portion of the device.

Figure 1.4: Bipolar device cross section [4]

## **1.2 Uses of Bipolar Transistors**

The primary uses of bipolar transistors and ICs are :-

As an amplifier (analog or linear). A small current is amplified to a much larger value by the transistor. Transistors used as amplifiers are usually operated in the small signal mode. In this mode, the changes in the currents flowing in the transistors are small compared to the bias currents. For linear applications, the individual process steps are modified to achieve higher device breakdown voltages and higher device current gains. This application typically requires thick epitaxial silicon layers and deep junctions.

As an electronic switch (logic or digital). A large current can be turned on or off by a small current. Transistors used as switches are operated in the large signal mode. In this mode, the transistor will typically be switched from cutoff to saturation. For digital applications, the individual process steps are modified to achieve the high packing density required for complex digital circuits. This application typically requires thin epitaxial silicon layers and shallow junction depth.

Both of these uses depend on the current amplification property of the bipolar transistor.

### **1.3 Statement of Problem**

PNP transistor fabrication cycle time is too long compared to the NPN transistor fabrication. On time delivery to customer is being affected by the PNP transistor fabrication due to additional steps in the process flow. Therefore, there is a need to find ways to reduce cycle time of the PNP transistor fabrication. Since boron steam consolidation to emitter diffusion has been identified as one of the potential and viable project, focus will only be to this consolidation project.

### 1.4 Objective of Project

The objective is to implement boron consolidation to emitter diffusion with minimum impact to manufacturing. Final electrical testing results have to be comparable. The new process should also meet reliability requirements.

### **1.5** Scope and Limitation

The scope of this project is limited to existing hardware that is already available. Due to this, there will be limitation to some of the experiments that can be carried out such as the steam temperature selection and post steam cleaning time.

## **1.6 Expected Outcome**

Since the wafer will not be subjected to any new material or processing, the outcome is expected to be positive. However due to the steam temperature increase, there could be some complications in final electrical response. This can be verified at final electrical testing.

### **CHAPTER 2**

### LITERATURE REVIEW

### 2.1 Introduction

Wafer fabrication is a very complex process whereby the entire process consists of many steps. In most cases these steps are repeated with different parameters. Proper sequencing and repetition of the oxidation, patterning and dopant addition operations can be used to introduce p- and n-type dopant atoms selectively into regions on a surface having dimensions ranging down to the submicron range. These steps are the basic elements of wafer fabrication [2]. In early process, before silicon, Germanium transistors were made by alloying the emitter and the collector regions to a thin slice of an appropriately doped semiconductor. This process did not allow good control of the emitter and collector geometries and resulted in base widths on the order of several microns. Consequently, in the beginning Silicon transistors were made by growing the emitter, base, and collector regions during the process of crystal growth from the melt. The next significant step was to develop a solid-state impurity diffusion process that allowed much tighter control over the device geometry and the base width. Alternatively, transistors could be produced by a double diffusion process in which p- and n-type diffusions were performed in succession from the same face of the wafer giving the impurity profiles needed [3].

A more commonly used process technology is the CMOS technology, whereby a totally different structure is fabricated, taking into consideration the requirement of today's needs. Low power consumption, low leakage requirements and low heat dissipation were among the motivations towards this change. Nevertheless the demands for bipolar is still increasing due to certain applications are performing better using this technology.

## 2.2 Bipolar Junction Transistor (BJT) Operations

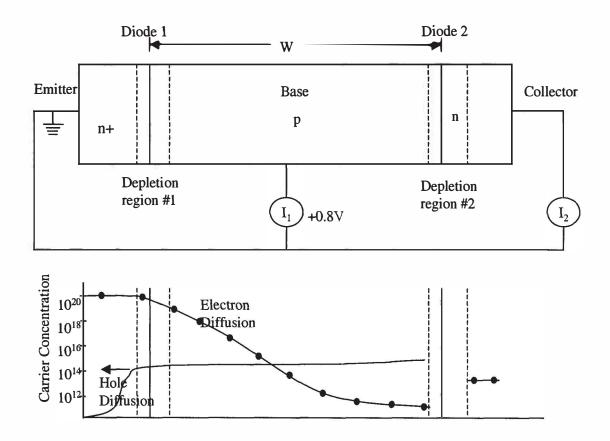

The operation of an NPN transistor is explained in Figure 2.1, two brick type junction diodes share a central p-type material of initial width, W.

Figure 2.1. Two brick diodes forming a bipolar transistor [1].